Item (NB Cont.) |

| Specification |

|

|

|

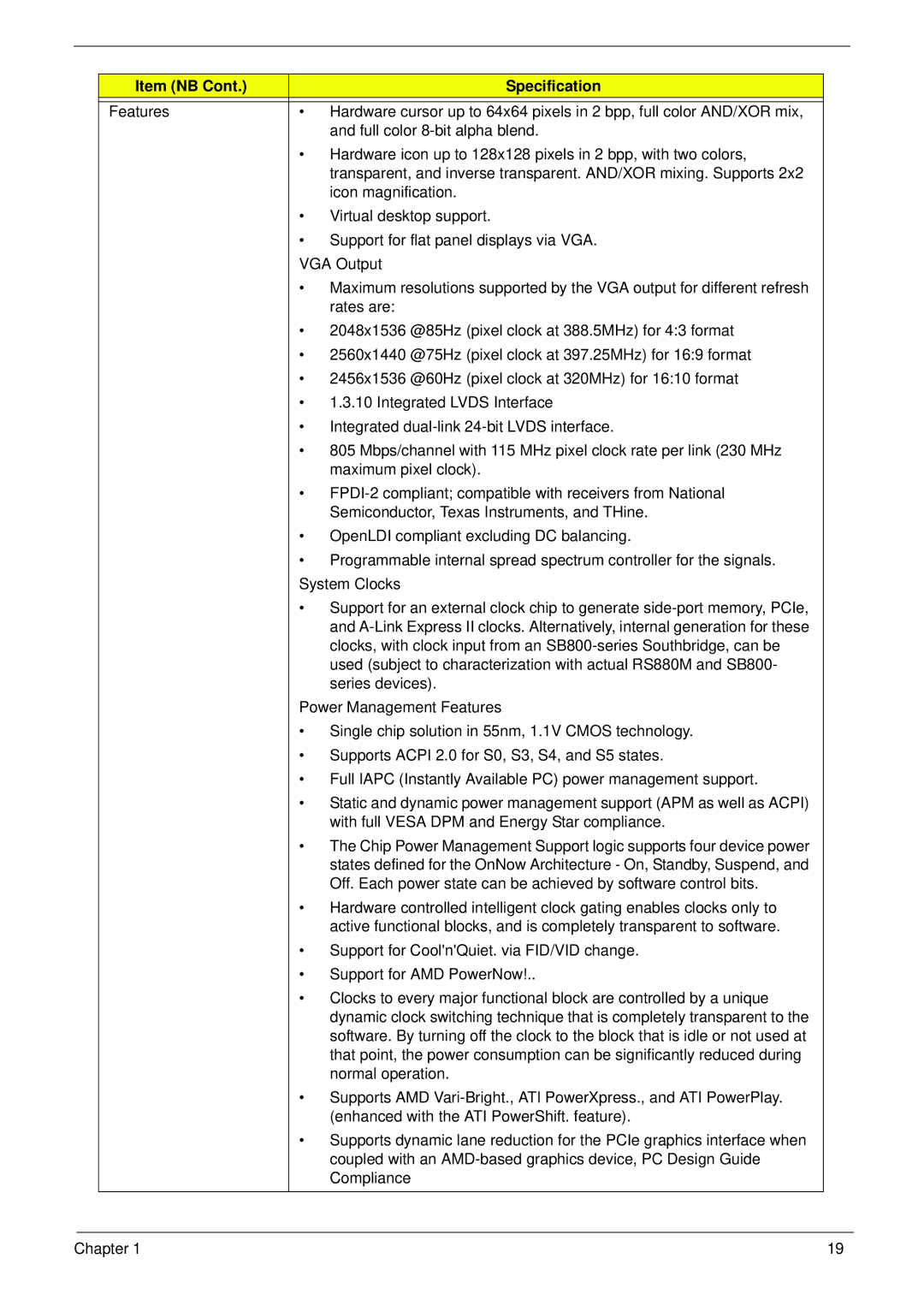

Features | • | Hardware cursor up to 64x64 pixels in 2 bpp, full color AND/XOR mix, |

|

| and full color |

| • Hardware icon up to 128x128 pixels in 2 bpp, with two colors, | |

|

| transparent, and inverse transparent. AND/XOR mixing. Supports 2x2 |

|

| icon magnification. |

| • | Virtual desktop support. |

| • Support for flat panel displays via VGA. | |

| VGA Output | |

| • Maximum resolutions supported by the VGA output for different refresh | |

|

| rates are: |

| • 2048x1536 @85Hz (pixel clock at 388.5MHz) for 4:3 format | |

| • 2560x1440 @75Hz (pixel clock at 397.25MHz) for 16:9 format | |

| • 2456x1536 @60Hz (pixel clock at 320MHz) for 16:10 format | |

| • 1.3.10 Integrated LVDS Interface | |

| • Integrated | |

| • 805 Mbps/channel with 115 MHz pixel clock rate per link (230 MHz | |

|

| maximum pixel clock). |

| • | |

|

| Semiconductor, Texas Instruments, and THine. |

| • OpenLDI compliant excluding DC balancing. | |

| • Programmable internal spread spectrum controller for the signals. | |

| System Clocks | |

| • Support for an external clock chip to generate | |

|

| and |

|

| clocks, with clock input from an |

|

| used (subject to characterization with actual RS880M and SB800- |

|

| series devices). |

| Power Management Features | |

| • Single chip solution in 55nm, 1.1V CMOS technology. | |

| • Supports ACPI 2.0 for S0, S3, S4, and S5 states. | |

| • Full IAPC (Instantly Available PC) power management support. | |

| • Static and dynamic power management support (APM as well as ACPI) | |

|

| with full VESA DPM and Energy Star compliance. |

| • The Chip Power Management Support logic supports four device power | |

|

| states defined for the OnNow Architecture - On, Standby, Suspend, and |

|

| Off. Each power state can be achieved by software control bits. |

| • Hardware controlled intelligent clock gating enables clocks only to | |

|

| active functional blocks, and is completely transparent to software. |

| • Support for Cool'n'Quiet. via FID/VID change. | |

| • Support for AMD PowerNow!.. | |

| • Clocks to every major functional block are controlled by a unique | |

|

| dynamic clock switching technique that is completely transparent to the |

|

| software. By turning off the clock to the block that is idle or not used at |

|

| that point, the power consumption can be significantly reduced during |

|

| normal operation. |

| • Supports AMD | |

|

| (enhanced with the ATI PowerShift. feature). |

| • Supports dynamic lane reduction for the PCIe graphics interface when | |

|

| coupled with an |

|

| Compliance |

|

|

|

Chapter 1 | 19 |