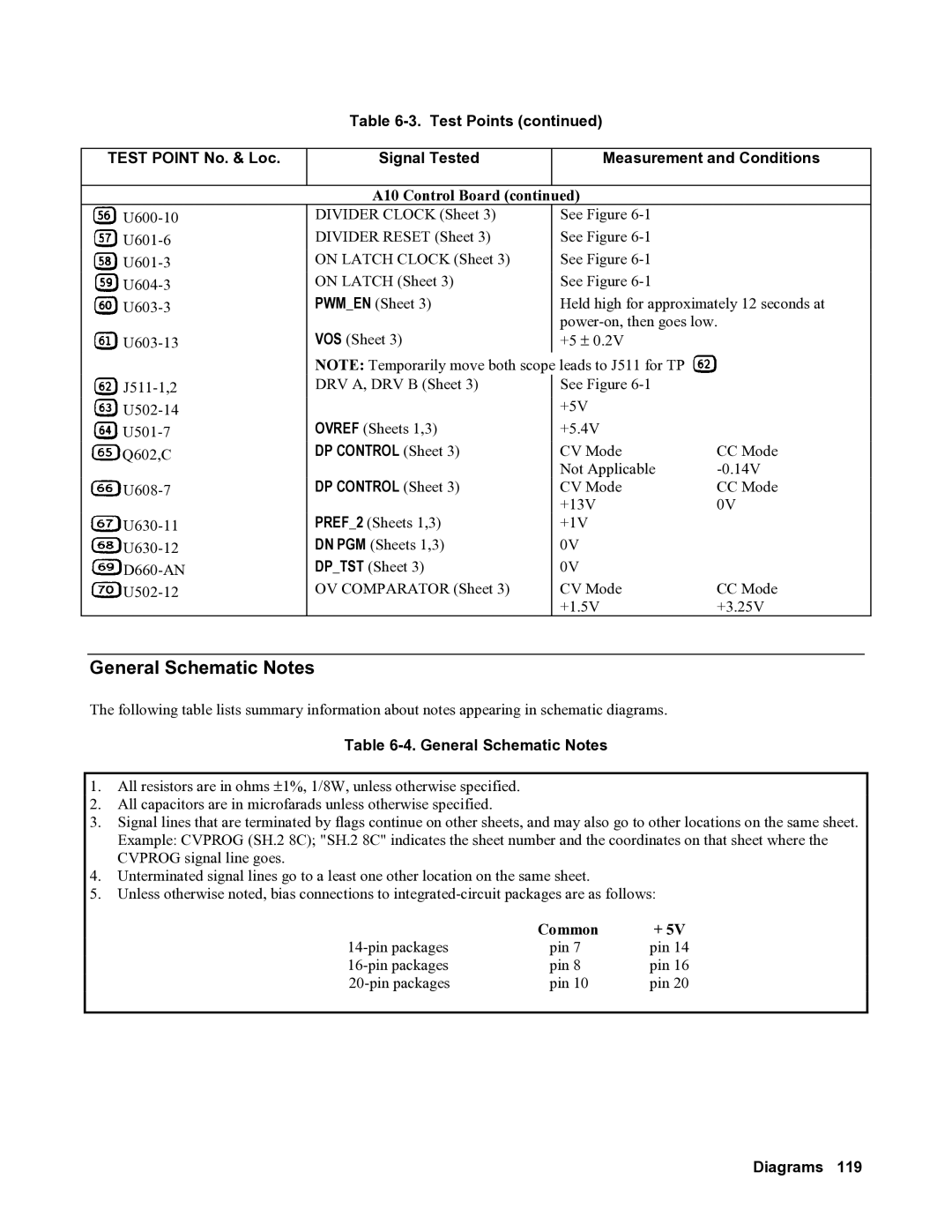

Table

| TEST POINT No. & Loc. | Signal Tested | Measurement and Conditions | ||

|

|

|

|

|

|

|

|

| A10 Control Board (continued) |

| |

|

| DIVIDER CLOCK (Sheet 3) | See Figure |

| |

|

| DIVIDER RESET (Sheet 3) | See Figure |

| |

|

| ON LATCH CLOCK (Sheet 3) | See Figure |

| |

|

| ON LATCH (Sheet 3) | See Figure |

| |

|

| PWM_EN (Sheet 3) | Held high for approximately 12 seconds at | ||

|

| ||||

|

|

| VOS (Sheet 3) | ||

|

| +5 ± 0.2V |

| ||

|

|

| NOTE: Temporarily move both scope leads to J511 for TP |

| |

|

| DRV A, DRV B (Sheet 3) | See Figure |

| |

|

| OVREF (Sheets 1,3) | +5V |

| |

| +5.4V |

| |||

| Q602,C | DP CONTROL (Sheet 3) | CV Mode | CC Mode | |

|

|

| DP CONTROL (Sheet 3) | Not Applicable | |

|

| CV Mode | CC Mode | ||

|

|

| PREF_2 (Sheets 1,3) | +13V | 0V |

|

| +1V |

| ||

|

| DN PGM (Sheets 1,3) | 0V |

| |

|

| DP_TST (Sheet 3) | 0V |

| |

|

|

| |||

|

| OV COMPARATOR (Sheet 3) | CV Mode | CC Mode | |

|

|

|

| +1.5V | +3.25V |

General Schematic Notes

The following table lists summary information about notes appearing in schematic diagrams.

Table 6-4. General Schematic Notes

1.All resistors are in ohms ±1%, 1/8W, unless otherwise specified.

2.All capacitors are in microfarads unless otherwise specified.

3.Signal lines that are terminated by flags continue on other sheets, and may also go to other locations on the same sheet. Example: CVPROG (SH.2 8C); "SH.2 8C" indicates the sheet number and the coordinates on that sheet where the CVPROG signal line goes.

4.Unterminated signal lines go to a least one other location on the same sheet.

5.Unless otherwise noted, bias connections to

| Common | + 5V |

pin 7 | pin 14 | |

pin 8 | pin 16 | |

pin 10 | pin 20 |