3.4Using the SDRAM Interface

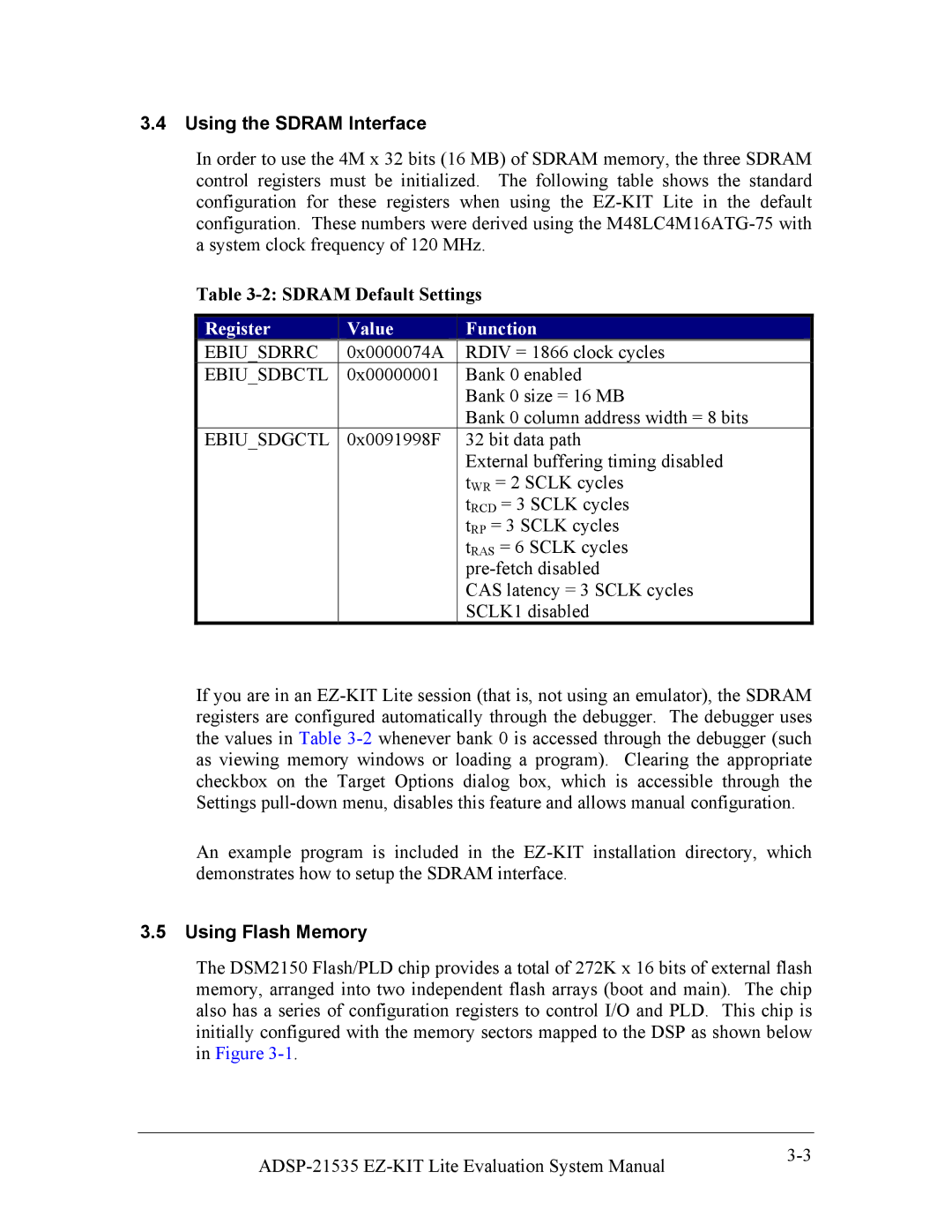

In order to use the 4M x 32 bits (16 MB) of SDRAM memory, the three SDRAM control registers must be initialized. The following table shows the standard configuration for these registers when using the

Table

Register | Value | Function |

EBIU_SDRRC | 0x0000074A | RDIV = 1866 clock cycles |

EBIU_SDBCTL | 0x00000001 | Bank 0 enabled |

|

| Bank 0 size = 16 MB |

|

| Bank 0 column address width = 8 bits |

EBIU_SDGCTL | 0x0091998F | 32 bit data path |

|

| External buffering timing disabled |

|

| tWR = 2 SCLK cycles |

|

| tRCD = 3 SCLK cycles |

|

| tRP = 3 SCLK cycles |

|

| tRAS = 6 SCLK cycles |

|

| |

|

| CAS latency = 3 SCLK cycles |

|

| SCLK1 disabled |

If you are in an

An example program is included in the

3.5Using Flash Memory

The DSM2150 Flash/PLD chip provides a total of 272K x 16 bits of external flash memory, arranged into two independent flash arrays (boot and main). The chip also has a series of configuration registers to control I/O and PLD. This chip is initially configured with the memory sectors mapped to the DSP as shown below in Figure

|