3.6Using the Programmable Flag Pins

The

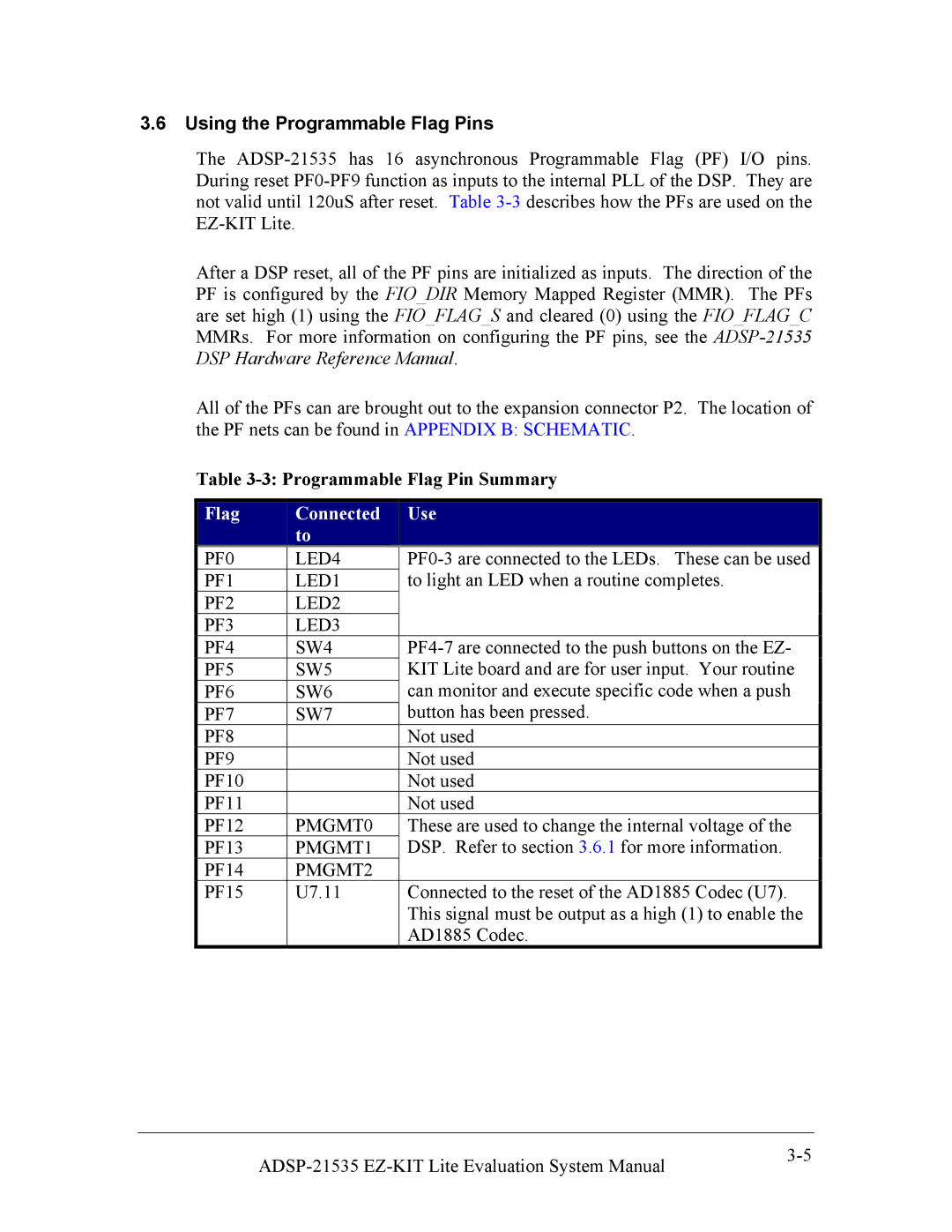

After a DSP reset, all of the PF pins are initialized as inputs. The direction of the PF is configured by the FIO_DIR Memory Mapped Register (MMR). The PFs are set high (1) using the FIO_FLAG_S and cleared (0) using the FIO_FLAG_C MMRs. For more information on configuring the PF pins, see the

All of the PFs can are brought out to the expansion connector P2. The location of the PF nets can be found in APPENDIX B: SCHEMATIC.

Table

Flag | Connected |

| Use |

|

| to |

|

|

|

PF0 | LED4 |

|

| |

PF1 | LED1 |

| to light an LED when a routine completes. |

|

PF2 | LED2 |

|

|

|

PF3 | LED3 |

|

|

|

PF4 | SW4 |

|

| |

PF5 | SW5 |

| KIT Lite board and are for user input. Your routine |

|

PF6 | SW6 |

| can monitor and execute specific code when a push |

|

PF7 | SW7 |

| button has been pressed. |

|

PF8 |

|

| Not used |

|

PF9 |

|

| Not used |

|

PF10 |

|

| Not used |

|

PF11 |

|

| Not used |

|

PF12 | PMGMT0 |

| These are used to change the internal voltage of the |

|

PF13 | PMGMT1 |

| DSP. Refer to section 3.6.1 for more information. |

|

PF14 | PMGMT2 |

|

|

|

PF15 | U7.11 |

| Connected to the reset of the AD1885 Codec (U7). |

|

|

|

| This signal must be output as a high (1) to enable the |

|

|

|

| AD1885 Codec. |

|

|