|

|

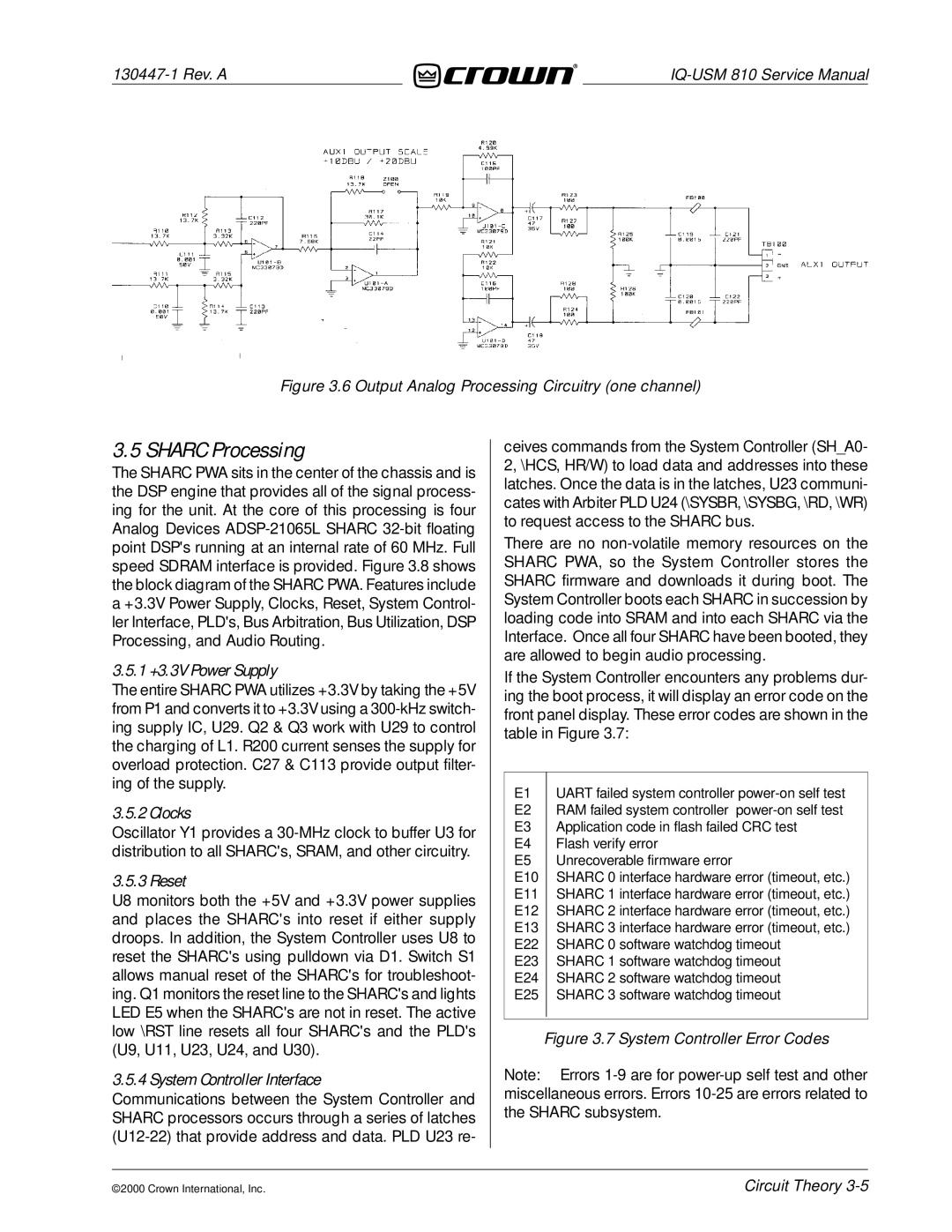

Figure 3.6 Output Analog Processing Circuitry (one channel)

3.5 SHARC Processing

The SHARC PWA sits in the center of the chassis and is the DSP engine that provides all of the signal process- ing for the unit. At the core of this processing is four Analog Devices

3.5.1 +3.3V Power Supply

The entire SHARC PWA utilizes +3.3V by taking the +5V from P1 and converts it to +3.3V using a

3.5.2 Clocks

Oscillator Y1 provides a

3.5.3 Reset

U8 monitors both the +5V and +3.3V power supplies and places the SHARC's into reset if either supply droops. In addition, the System Controller uses U8 to reset the SHARC's using pulldown via D1. Switch S1 allows manual reset of the SHARC's for troubleshoot- ing. Q1 monitors the reset line to the SHARC's and lights LED E5 when the SHARC's are not in reset. The active low \RST line resets all four SHARC's and the PLD's (U9, U11, U23, U24, and U30).

3.5.4 System Controller Interface

Communications between the System Controller and SHARC processors occurs through a series of latches

ceives commands from the System Controller (SH_A0- 2, \HCS, HR/W) to load data and addresses into these latches. Once the data is in the latches, U23 communi- cates with Arbiter PLD U24 (\SYSBR, \SYSBG, \RD, \WR) to request access to the SHARC bus.

There are no

If the System Controller encounters any problems dur- ing the boot process, it will display an error code on the front panel display. These error codes are shown in the table in Figure 3.7:

E1 | UART failed system controller |

E2 | RAM failed system controller |

E3 | Application code in flash failed CRC test |

E4 | Flash verify error |

E5 | Unrecoverable firmware error |

E10 | SHARC 0 interface hardware error (timeout, etc.) |

E11 | SHARC 1 interface hardware error (timeout, etc.) |

E12 | SHARC 2 interface hardware error (timeout, etc.) |

E13 | SHARC 3 interface hardware error (timeout, etc.) |

E22 | SHARC 0 software watchdog timeout |

E23 | SHARC 1 software watchdog timeout |

E24 | SHARC 2 software watchdog timeout |

E25 | SHARC 3 software watchdog timeout |

|

|

Figure 3.7 System Controller Error Codes

Note: Errors

©2000 Crown International, Inc.

Circuit Theory