The System Controller will display the error code, then begin the boot process again. By watching the boot process on the front display, the error code can be read at the end of the boot process before the next boot be- gins.

3.5.5 PLDs

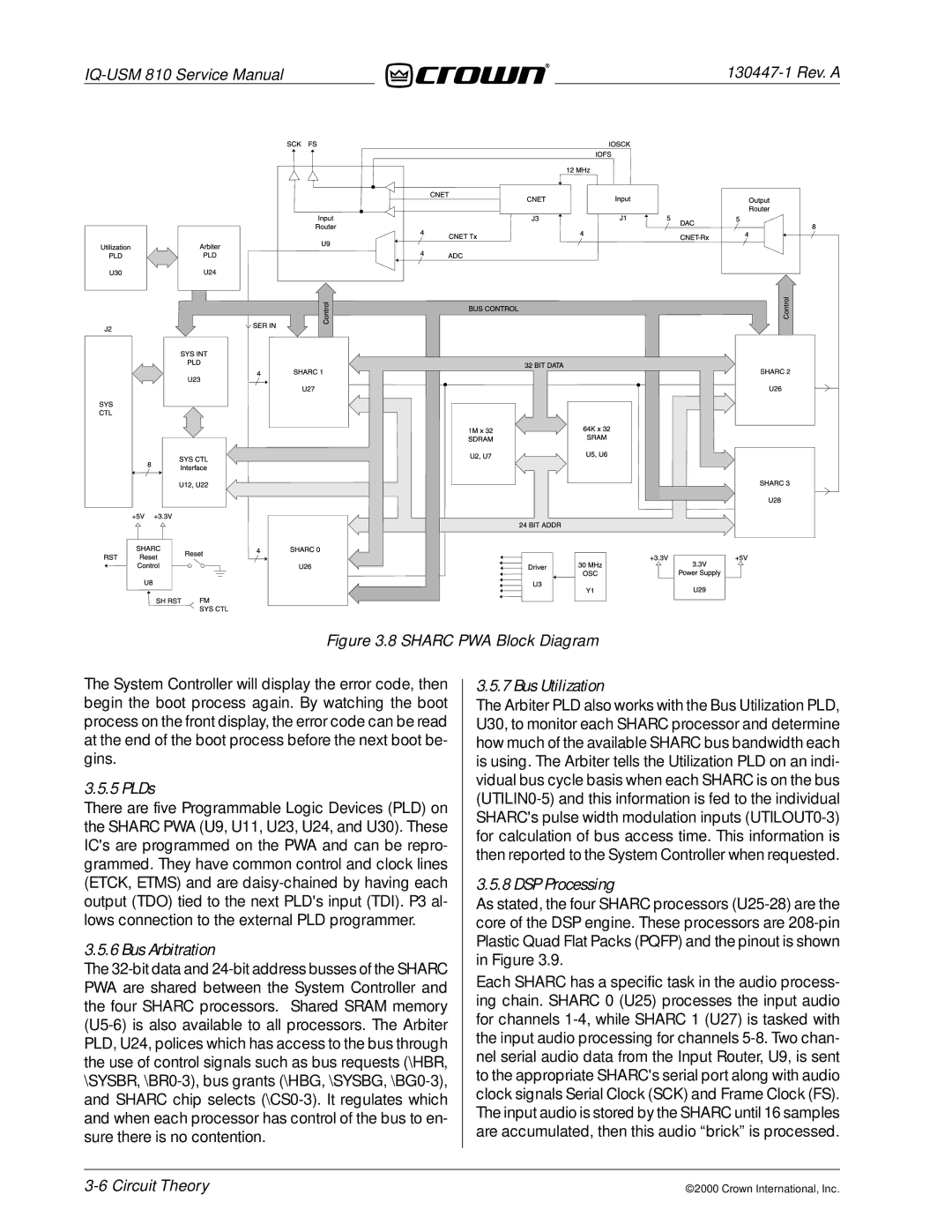

There are five Programmable Logic Devices (PLD) on the SHARC PWA (U9, U11, U23, U24, and U30). These IC's are programmed on the PWA and can be repro- grammed. They have common control and clock lines (ETCK, ETMS) and are daisy-chained by having each output (TDO) tied to the next PLD's input (TDI). P3 al- lows connection to the external PLD programmer.

3.5.6 Bus Arbitration

The 32-bit data and 24-bit address busses of the SHARC PWA are shared between the System Controller and the four SHARC processors. Shared SRAM memory (U5-6) is also available to all processors. The Arbiter PLD, U24, polices which has access to the bus through the use of control signals such as bus requests (\HBR, \SYSBR, \BR0-3), bus grants (\HBG, \SYSBG, \BG0-3), and SHARC chip selects (\CS0-3). It regulates which and when each processor has control of the bus to en- sure there is no contention.

3.5.7 Bus Utilization

The Arbiter PLD also works with the Bus Utilization PLD, U30, to monitor each SHARC processor and determine how much of the available SHARC bus bandwidth each is using. The Arbiter tells the Utilization PLD on an indi- vidual bus cycle basis when each SHARC is on the bus (UTILIN0-5) and this information is fed to the individual SHARC's pulse width modulation inputs (UTILOUT0-3) for calculation of bus access time. This information is then reported to the System Controller when requested.

3.5.8 DSP Processing

As stated, the four SHARC processors (U25-28) are the core of the DSP engine. These processors are 208-pin Plastic Quad Flat Packs (PQFP) and the pinout is shown in Figure 3.9.

Each SHARC has a specific task in the audio process- ing chain. SHARC 0 (U25) processes the input audio for channels 1-4, while SHARC 1 (U27) is tasked with the input audio processing for channels 5-8. Two chan- nel serial audio data from the Input Router, U9, is sent to the appropriate SHARC's serial port along with audio clock signals Serial Clock (SCK) and Frame Clock (FS). The input audio is stored by the SHARC until 16 samples are accumulated, then this audio “brick” is processed.