CY7C64215

Applications

■PC HID devices

❐Mouse (Optomechanical, Optical, Trackball)

❐Keyboards

❐Joysticks

■Gaming

❐Game Pads

❐Console Keyboards

■General Purpose

❐Barcode Scanners

❐POS Terminal

❐Consumer Electronics

❐Toys

❐Remote Controls

❐USB to Serial

enCoRe III Functional Overview

The enCoRe III is based on flexible PSoC architecture and is a

This architecture allows the user to create customized peripheral configurations that match the requirements of each individual application. Additionally, a fast CPU, Flash program memory, SRAM data memory, and configurable IO are included in both

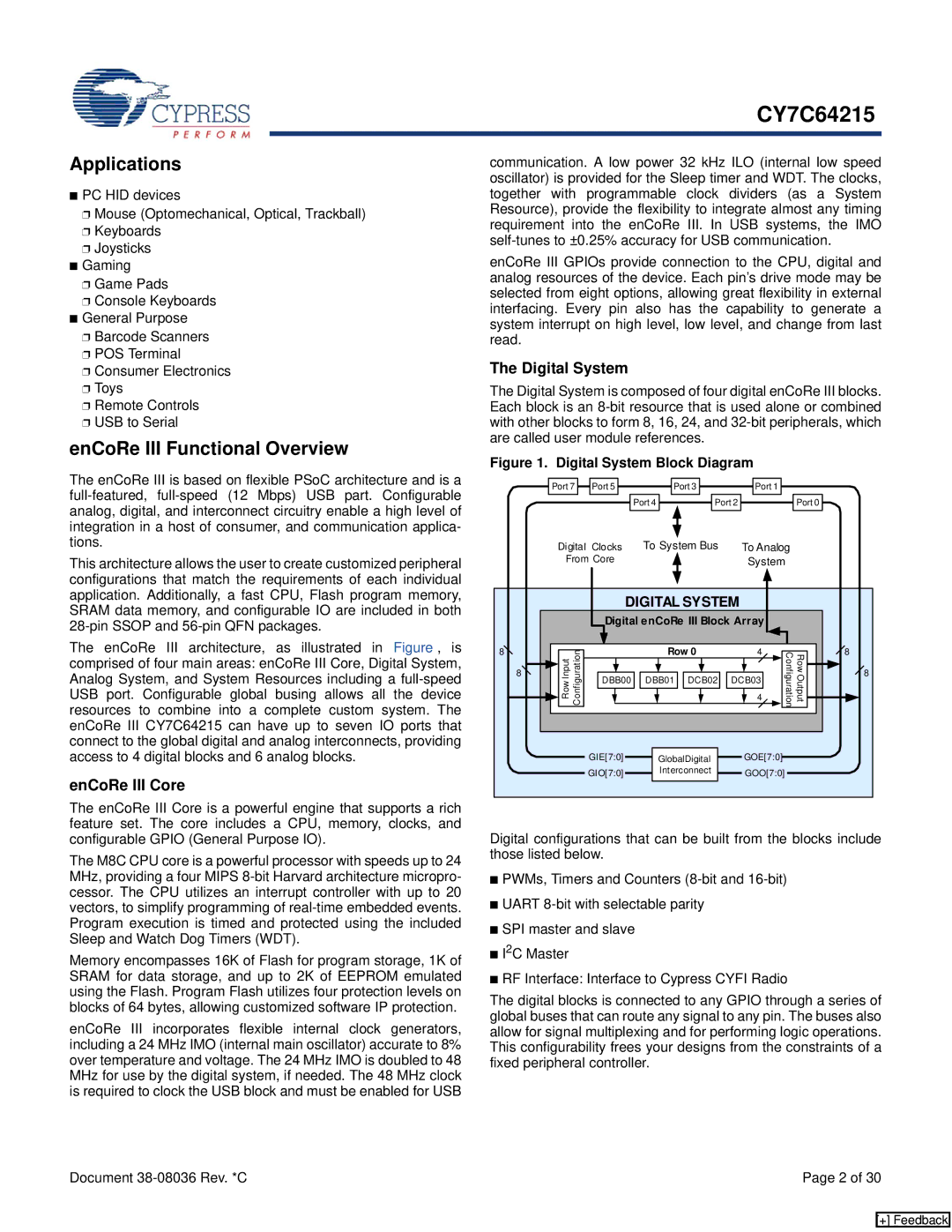

The enCoRe III architecture, as illustrated in Figure , is comprised of four main areas: enCoRe III Core, Digital System, Analog System, and System Resources including a

enCoRe III Core

The enCoRe III Core is a powerful engine that supports a rich feature set. The core includes a CPU, memory, clocks, and configurable GPIO (General Purpose IO).

The M8C CPU core is a powerful processor with speeds up to 24 MHz, providing a four MIPS

Memory encompasses 16K of Flash for program storage, 1K of SRAM for data storage, and up to 2K of EEPROM emulated using the Flash. Program Flash utilizes four protection levels on blocks of 64 bytes, allowing customized software IP protection.

enCoRe III incorporates flexible internal clock generators, including a 24 MHz IMO (internal main oscillator) accurate to 8% over temperature and voltage. The 24 MHz IMO is doubled to 48 MHz for use by the digital system, if needed. The 48 MHz clock is required to clock the USB block and must be enabled for USB

communication. A low power 32 kHz ILO (internal low speed oscillator) is provided for the Sleep timer and WDT. The clocks, together with programmable clock dividers (as a System Resource), provide the flexibility to integrate almost any timing requirement into the enCoRe III. In USB systems, the IMO

enCoRe III GPIOs provide connection to the CPU, digital and analog resources of the device. Each pin’s drive mode may be selected from eight options, allowing great flexibility in external interfacing. Every pin also has the capability to generate a system interrupt on high level, low level, and change from last read.

The Digital System

The Digital System is composed of four digital enCoRe III blocks. Each block is an

Figure 1. Digital System Block Diagram

Port 7 |

| Port 5 |

|

|

| Port 3 |

|

|

| Port 1 |

|

|

|

|

|

| Port 4 |

|

|

| Port 2 |

|

|

| Port 0 |

Digital | Clocks | To System Bus | To Analog |

| ||

From Core |

|

| System |

|

| |

|

|

|

|

|

| |

| DIGITAL SYSTEM |

|

| |||

| Digital enCoRe III Block Array |

|

| |||

8 |

| Row 0 | 4 |

| 8 | |

8 | DBB00 | DBB01 | DCB02 | DCB03 |

| 8 |

RowInput Configuration | RowOutput Configuration |

| ||||

|

|

| 4 |

| ||

| GIE[7:0] | GlobalDigital | GOE[7:0] |

|

| |

| GIO[7:0] | Interconnect | GOO[7:0] |

|

| |

|

|

|

|

| ||

Digital configurations that can be built from the blocks include those listed below.

■PWMs, Timers and Counters

■UART

■SPI master and slave

■I2C Master

■RF Interface: Interface to Cypress CYFI Radio

The digital blocks is connected to any GPIO through a series of global buses that can route any signal to any pin. The buses also allow for signal multiplexing and for performing logic operations. This configurability frees your designs from the constraints of a fixed peripheral controller.

Document | Page 2 of 30 |

[+] Feedback