1

Board Description and Memory Maps

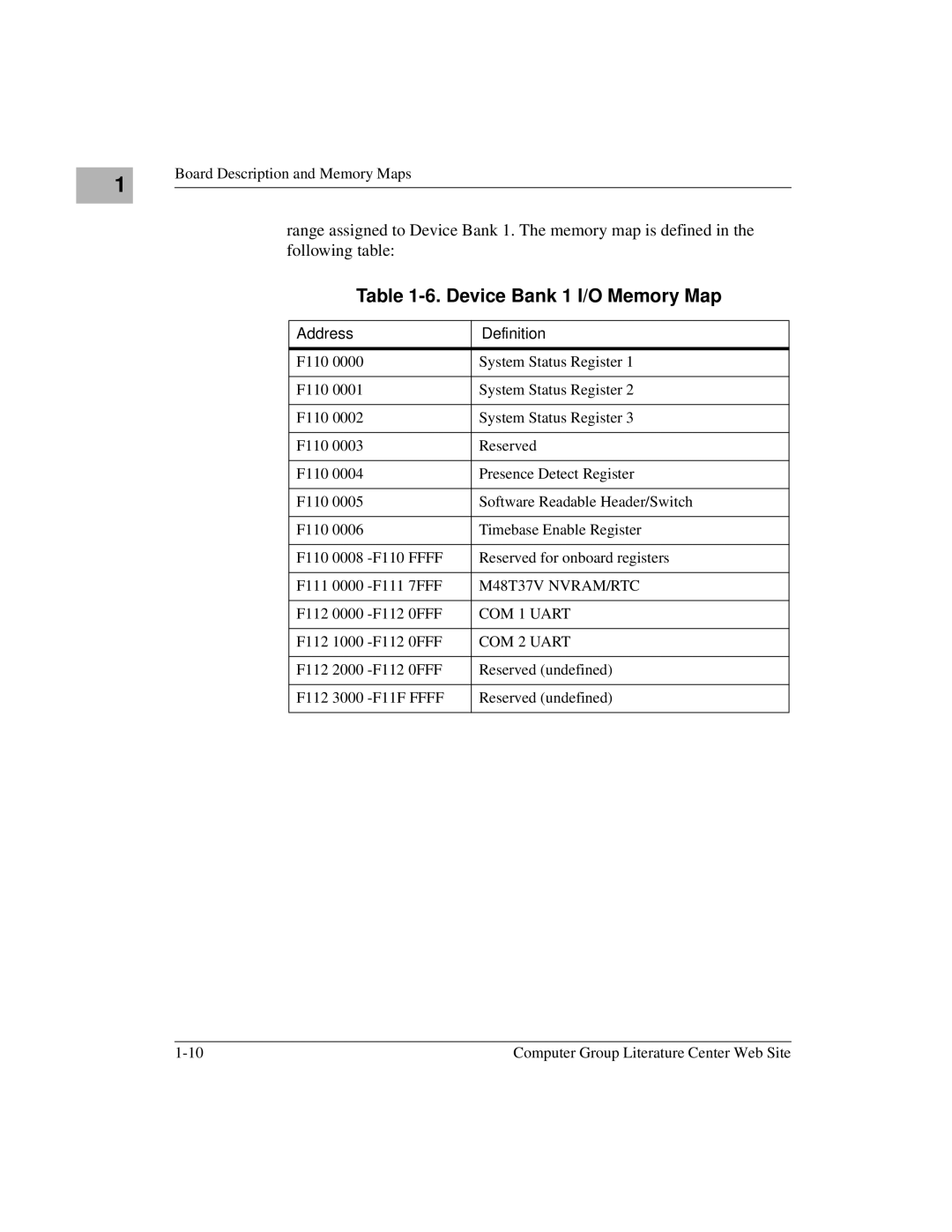

range assigned to Device Bank 1. The memory map is defined in the following table:

Table 1-6. Device Bank 1 I/O Memory Map

Address |

| Definition | |

|

|

| |

F110 0000 |

| System Status Register 1 | |

|

|

| |

F110 0001 |

| System Status Register 2 | |

|

|

| |

F110 0002 |

| System Status Register 3 | |

|

|

|

|

F110 | 0003 |

| Reserved |

|

|

|

|

F110 | 0004 |

| Presence Detect Register |

|

|

|

|

F110 | 0005 |

| Software Readable Header/Switch |

|

|

|

|

F110 | 0006 |

| Timebase Enable Register |

|

|

|

|

F110 | 0008 | Reserved for onboard registers | |

|

|

|

|

F111 | 0000 | M48T37V NVRAM/RTC | |

|

|

|

|

F112 | 0000 | COM 1 UART | |

|

|

|

|

F112 | 1000 | COM 2 UART | |

|

|

|

|

F112 | 2000 | Reserved (undefined) | |

|

|

|

|

F112 | 3000 | Reserved (undefined) | |

|

|

|

|

Computer Group Literature Center Web Site |