Programming Details

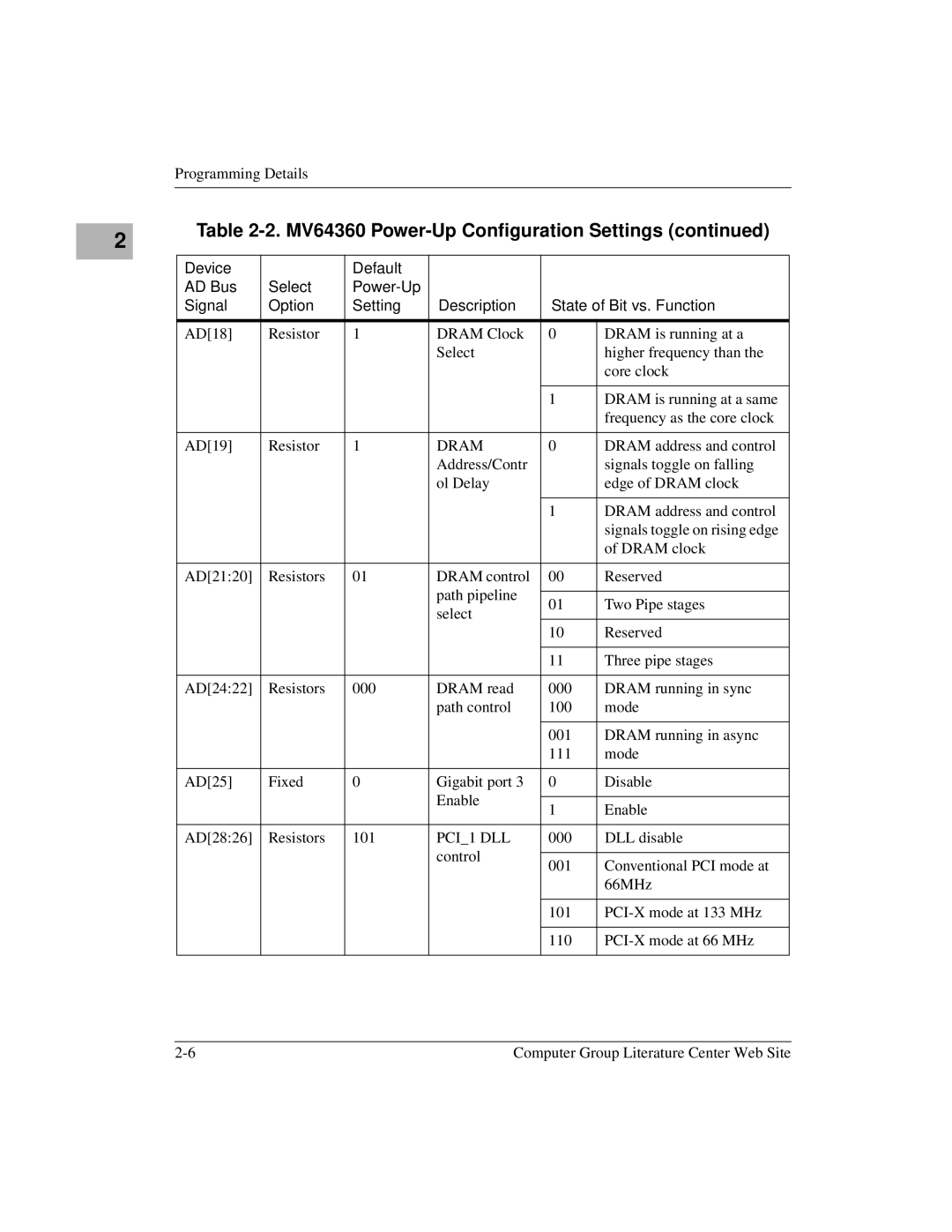

2Table 2-2. MV64360 Power-Up Configuration Settings (continued)

Device |

| Default |

|

|

|

AD Bus | Select |

|

|

| |

Signal | Option | Setting | Description | State of Bit vs. Function | |

|

|

|

|

|

|

AD[18] | Resistor | 1 | DRAM Clock | 0 | DRAM is running at a |

|

|

| Select |

| higher frequency than the |

|

|

|

|

| core clock |

|

|

|

|

|

|

|

|

|

| 1 | DRAM is running at a same |

|

|

|

|

| frequency as the core clock |

|

|

|

|

|

|

AD[19] | Resistor | 1 | DRAM | 0 | DRAM address and control |

|

|

| Address/Contr |

| signals toggle on falling |

|

|

| ol Delay |

| edge of DRAM clock |

|

|

|

|

|

|

|

|

|

| 1 | DRAM address and control |

|

|

|

|

| signals toggle on rising edge |

|

|

|

|

| of DRAM clock |

|

|

|

|

|

|

AD[21:20] | Resistors | 01 | DRAM control | 00 | Reserved |

|

|

| path pipeline |

|

|

|

|

| 01 | Two Pipe stages | |

|

|

| select | ||

|

|

|

|

| |

|

|

|

| 10 | Reserved |

|

|

|

|

|

|

|

|

|

| 11 | Three pipe stages |

|

|

|

|

|

|

AD[24:22] | Resistors | 000 | DRAM read | 000 | DRAM running in sync |

|

|

| path control | 100 | mode |

|

|

|

|

|

|

|

|

|

| 001 | DRAM running in async |

|

|

|

| 111 | mode |

|

|

|

|

|

|

AD[25] | Fixed | 0 | Gigabit port 3 | 0 | Disable |

|

|

| Enable |

|

|

|

|

| 1 | Enable | |

|

|

|

| ||

|

|

|

|

|

|

AD[28:26] | Resistors | 101 | PCI_1 DLL | 000 | DLL disable |

|

|

| control |

|

|

|

|

| 001 | Conventional PCI mode at | |

|

|

|

| ||

|

|

|

|

| 66MHz |

|

|

|

|

|

|

|

|

|

| 101 | |

|

|

|

|

|

|

|

|

|

| 110 | |

|

|

|

|

|

|

Computer Group Literature Center Web Site |