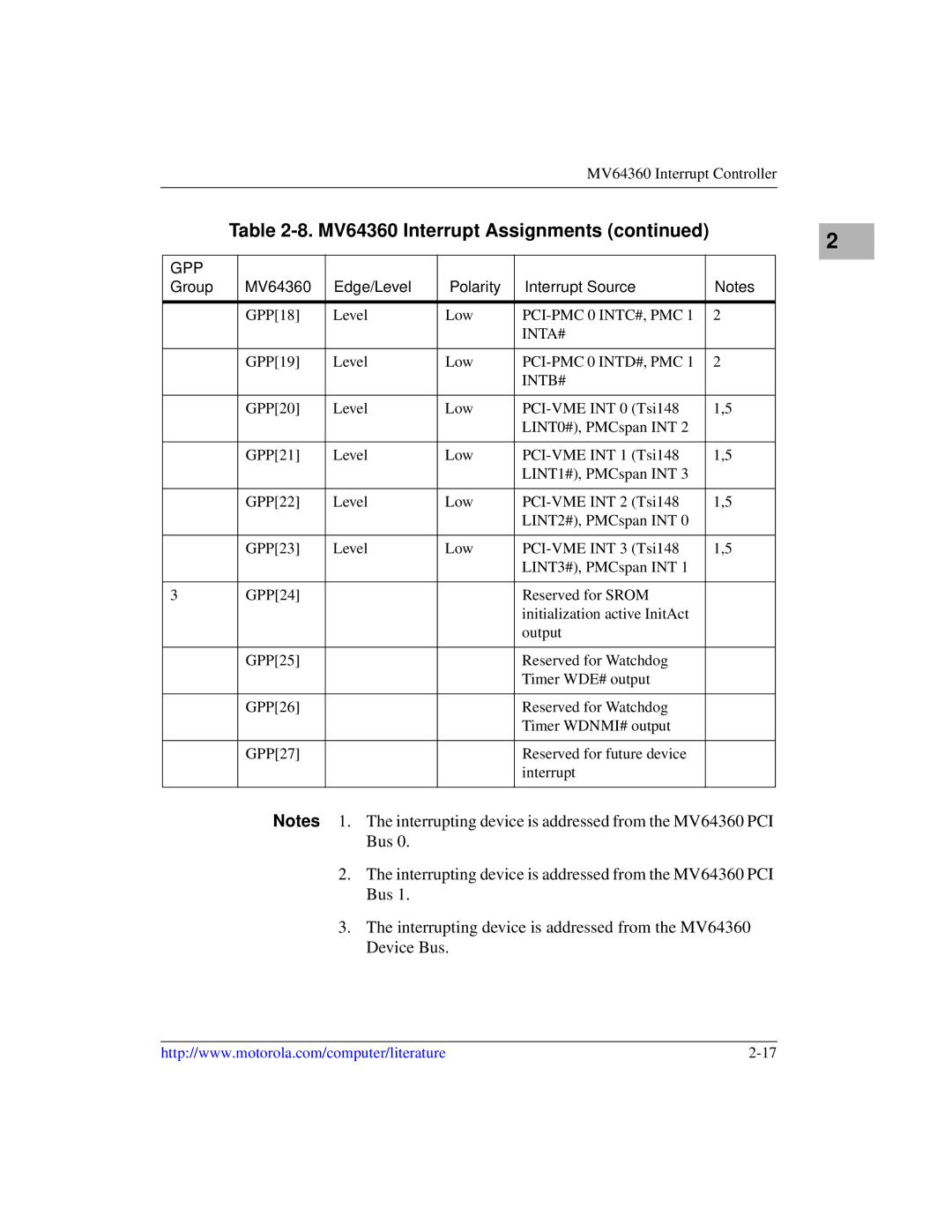

MV64360 Interrupt Controller

| Table |

|

|

| 2 | |||||

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

GPP |

|

|

|

|

|

|

|

|

|

|

Group |

| MV64360 | Edge/Level | Polarity | Interrupt Source |

| Notes |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| GPP[18] | Level | Low |

|

| 2 |

|

|

|

|

|

|

|

| INTA# |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GPP[19] | Level | Low |

|

| 2 |

|

|

|

|

|

|

|

| INTB# |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GPP[20] | Level | Low |

| 1,5 |

|

|

| |

|

|

|

|

| LINT0#), PMCspan INT 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GPP[21] | Level | Low |

| 1,5 |

|

|

| |

|

|

|

|

| LINT1#), PMCspan INT 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GPP[22] | Level | Low |

| 1,5 |

|

|

| |

|

|

|

|

| LINT2#), PMCspan INT 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GPP[23] | Level | Low |

| 1,5 |

|

|

| |

|

|

|

|

| LINT3#), PMCspan INT 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

| GPP[24] |

|

| Reserved for SROM |

|

|

|

|

|

|

|

|

|

| initialization active InitAct |

|

|

|

|

|

|

|

|

|

| output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GPP[25] |

|

| Reserved for Watchdog |

|

|

|

|

|

|

|

|

|

| Timer WDE# output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GPP[26] |

|

| Reserved for Watchdog |

|

|

|

|

|

|

|

|

|

| Timer WDNMI# output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GPP[27] |

|

| Reserved for future device |

|

|

|

|

|

|

|

|

|

| interrupt |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Notes 1. The interrupting device is addressed from the MV64360 PCI

Bus 0.

2.The interrupting device is addressed from the MV64360 PCI Bus 1.

3.The interrupting device is addressed from the MV64360 Device Bus.

http://www.motorola.com/computer/literature |