Time Base Enable Register

Time Base Enable Register

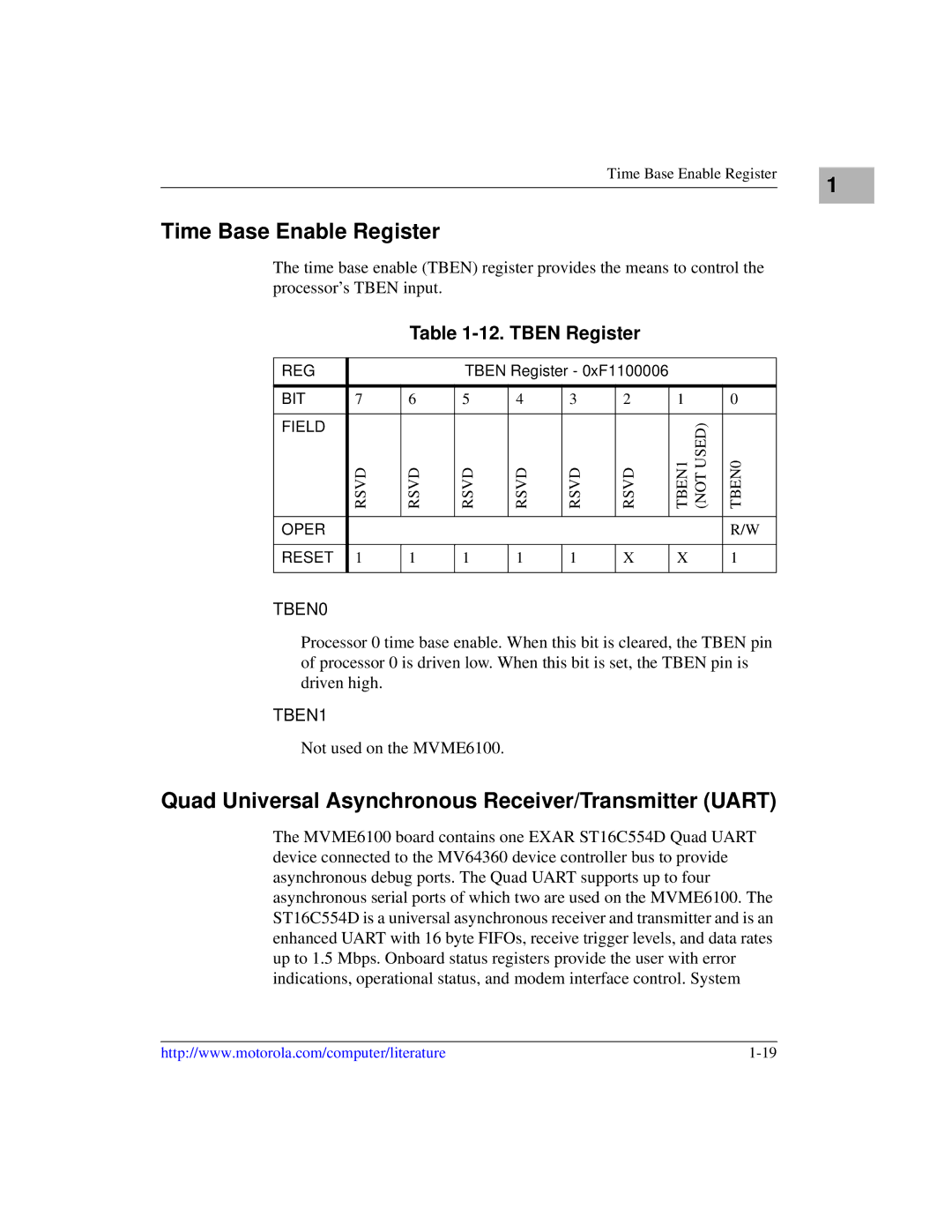

The time base enable (TBEN) register provides the means to control the processor’s TBEN input.

Table 1-12. TBEN Register

REG |

|

| TBEN Register - 0xF1100006 |

|

| |||

|

|

|

|

|

|

|

|

|

BIT | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

FIELD |

|

|

|

|

|

| TBEN1 (NOT USED) |

|

| RSVD | RSVD | RSVD | RSVD | RSVD | RSVD | TBEN0 | |

|

|

|

|

|

|

|

|

|

OPER |

|

|

|

|

|

|

| R/W |

|

|

|

|

|

|

|

|

|

RESET | 1 | 1 | 1 | 1 | 1 | X | X | 1 |

|

|

|

|

|

|

|

|

|

TBEN0

Processor 0 time base enable. When this bit is cleared, the TBEN pin of processor 0 is driven low. When this bit is set, the TBEN pin is driven high.

TBEN1

Not used on the MVME6100.

1

Quad Universal Asynchronous Receiver/Transmitter (UART)

The MVME6100 board contains one EXAR ST16C554D Quad UART device connected to the MV64360 device controller bus to provide asynchronous debug ports. The Quad UART supports up to four asynchronous serial ports of which two are used on the MVME6100. The ST16C554D is a universal asynchronous receiver and transmitter and is an enhanced UART with 16 byte FIFOs, receive trigger levels, and data rates up to 1.5 Mbps. Onboard status registers provide the user with error indications, operational status, and modem interface control. System

http://www.motorola.com/computer/literature |