AN50APPLICATION NOTE

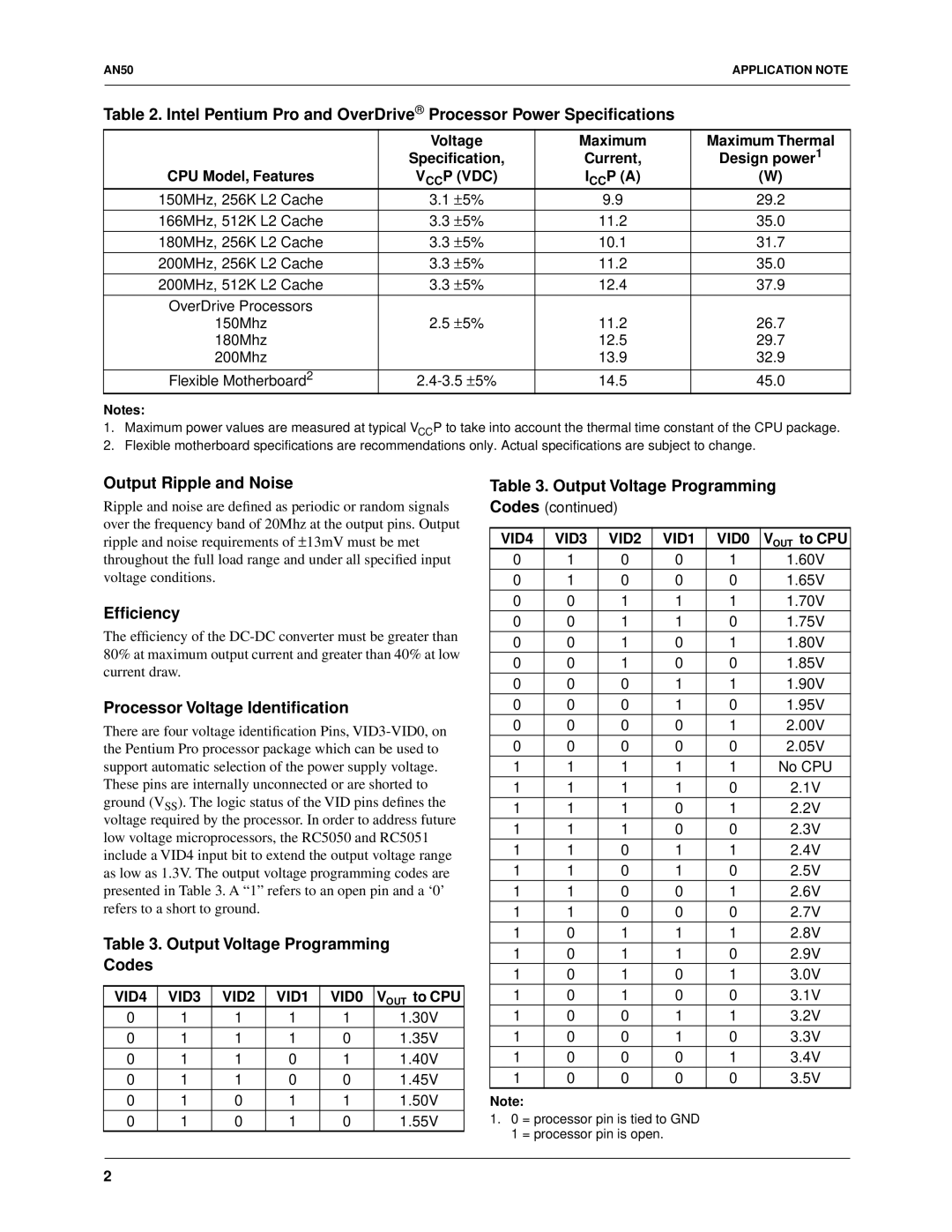

Table 2. Intel Pentium Pro and OverDrive® Processor Power Specifications

| Voltage | Maximum | Maximum Thermal |

| Specification, | Current, | Design power1 |

CPU Model, Features | VCCP (VDC) | ICCP (A) | (W) |

150MHz, 256K L2 Cache | 3.1 ±5% | 9.9 | 29.2 |

|

|

|

|

166MHz, 512K L2 Cache | 3.3 ±5% | 11.2 | 35.0 |

|

|

|

|

180MHz, 256K L2 Cache | 3.3 ±5% | 10.1 | 31.7 |

200MHz, 256K L2 Cache | 3.3 ±5% | 11.2 | 35.0 |

|

|

|

|

200MHz, 512K L2 Cache | 3.3 ±5% | 12.4 | 37.9 |

|

|

|

|

OverDrive Processors | 2.5 ±5% |

|

|

150Mhz | 11.2 | 26.7 | |

180Mhz |

| 12.5 | 29.7 |

200Mhz |

| 13.9 | 32.9 |

|

|

|

|

Flexible Motherboard2 | 14.5 | 45.0 |

Notes:

1.Maximum power values are measured at typical VCCP to take into account the thermal time constant of the CPU package.

2.Flexible motherboard specifications are recommendations only. Actual specifications are subject to change.

Output Ripple and Noise

Ripple and noise are defined as periodic or random signals over the frequency band of 20Mhz at the output pins. Output ripple and noise requirements of ±13mV must be met throughout the full load range and under all specified input voltage conditions.

Efficiency

The efficiency of the

Processor Voltage Identification

There are four voltage identification Pins,

Table 3. Output Voltage Programming Codes

VID4 | VID3 | VID2 | VID1 | VID0 | VOUT to CPU |

0 | 1 | 1 | 1 | 1 | 1.30V |

0 | 1 | 1 | 1 | 0 | 1.35V |

0 | 1 | 1 | 0 | 1 | 1.40V |

0 | 1 | 1 | 0 | 0 | 1.45V |

0 | 1 | 0 | 1 | 1 | 1.50V |

0 | 1 | 0 | 1 | 0 | 1.55V |

Table 3. Output Voltage Programming

Codes (continued)

VID4 | VID3 | VID2 | VID1 | VID0 | VOUT to CPU |

0 | 1 | 0 | 0 | 1 | 1.60V |

0 | 1 | 0 | 0 | 0 | 1.65V |

0 | 0 | 1 | 1 | 1 | 1.70V |

0 | 0 | 1 | 1 | 0 | 1.75V |

0 | 0 | 1 | 0 | 1 | 1.80V |

0 | 0 | 1 | 0 | 0 | 1.85V |

0 | 0 | 0 | 1 | 1 | 1.90V |

0 | 0 | 0 | 1 | 0 | 1.95V |

0 | 0 | 0 | 0 | 1 | 2.00V |

0 | 0 | 0 | 0 | 0 | 2.05V |

1 | 1 | 1 | 1 | 1 | No CPU |

1 | 1 | 1 | 1 | 0 | 2.1V |

1 | 1 | 1 | 0 | 1 | 2.2V |

1 | 1 | 1 | 0 | 0 | 2.3V |

1 | 1 | 0 | 1 | 1 | 2.4V |

1 | 1 | 0 | 1 | 0 | 2.5V |

1 | 1 | 0 | 0 | 1 | 2.6V |

1 | 1 | 0 | 0 | 0 | 2.7V |

1 | 0 | 1 | 1 | 1 | 2.8V |

1 | 0 | 1 | 1 | 0 | 2.9V |

1 | 0 | 1 | 0 | 1 | 3.0V |

1 | 0 | 1 | 0 | 0 | 3.1V |

1 | 0 | 0 | 1 | 1 | 3.2V |

1 | 0 | 0 | 1 | 0 | 3.3V |

1 | 0 | 0 | 0 | 1 | 3.4V |

1 | 0 | 0 | 0 | 0 | 3.5V |

Note:

1.0 = processor pin is tied to GND

1 = processor pin is open.

2