MHV2120AT, MHV2100AT, MHV2080AT MHV2060AT, MHV2040AT

Disk Drive Product Manual

For Safe Operation

Handling of This Manual

Revision History

This page is intentionally left blank

Preface

Overview of Manual

Conventions

Conventions for Alert Messages

Operating Environment

Liability Exception

This page is intentionally left blank

Damage Interface cable connection

Important Alert Items

Important Alert Messages

This page is intentionally left blank

Disk Drive Product Manual

Disk Drive Maintenance Manual

Manual Organization

This page is intentionally left blank

Contents

Installation Conditions

Theory of Device Operation

Contents

Interface

101

Write Multiple EXT X’39’ Option customizing

Operations

Glossary GL-1 Acronyms and Abbreviations AB-1 Index IN-1

Illustrations

Figures

Execution example of Read Multiple command

Surface temperature measurement points and standard

Tables

25 Relationship between combination of Identifier

This page is intentionally left blank

Device Overview

Adaptability

Features

Functions and performance

Error correction and retry by ECC

High resistance against shock

Connection to ATA interface

Data buffer

Specifications 1

Device Specifications

Specifications summary

Examples of model names and product numbers

Specifications 2

Model and product number

Ripple

Power Requirements

Input Voltage

Current Requirements and Power Dissipation

Current and power dissipation

Environmental Specifications

Current fluctuation Typ. at +5 V when power is turned on

Power on/off sequence

Environmental specifications

Acoustic noise specification

Shock and vibration specification

Acoustic Noise

Shock and Vibration

Service life

Data assurance in the event of power failure

Reliability

Mean time between failures Mtbf

Error Rate

Unrecoverable read error

Positioning error

Media Defects

Advanced Power Management

Advanced Power Management

Advanced Power Management

This page is intentionally left blank

Device Configuration

Device Configuration

System Configuration

ATA interface

2 1 drive connection

Read/write circuit

2 drives configuration

3 2 drives connection

Installation Conditions

Dimensions

Dimensions

Orientation

Mounting

Integration Guidance C141-E144

PCA

Frame

Limitation of mounting

Location of breather

Ambient temperature

Service area

Handling cautions

Handling cautions

Device connector

Cable Connections

Cable connector specifications

Cable connector specifications

Device connection

FCI

Location of setting jumpers

Jumper Settings

Power supply connector CN1

Factory default setting

Master drive-slave drive setting

Csel setting

14 Csel setting

Power up in standby setting

16 Example 2 of cable select

Theory of Device Operation

Outline

Subassemblies

Disk

Spindle

Circuit Configuration

Air filter

Servo circuit

Spindle motor driver circuit

Power supply configuration

PCA

Power-on Sequence

Power-on operation sequence

Self-calibration contents

Self-calibration

Command processing during self-calibration

Execution timing of self-calibration

Read/write Circuit

Read/write preamplifier PreAMP

Write circuit

Write precompensation

Programmable filter circuit

Read circuit

AGC circuit

Digital PLL circuit

FIR circuit

D converter circuit

Viterbi detection circuit

Servo Control

Servo control circuit

Power amplifier

Microprocessor unit MPU

Servo burst capture circuit

A converter DAC

Driver circuit

VCM current sense resistor CSR

Data-surface servo format

Inner guard band

Data area

Outer guard band

Physical sector servo configuration on disk surface

Servo frame format

Actuator motor control

Operation to move the head to the reference cylinder

Seek operation

Track following operation

Start mode

Acceleration mode

Stable rotation mode

Spindle motor control

This page is intentionally left blank

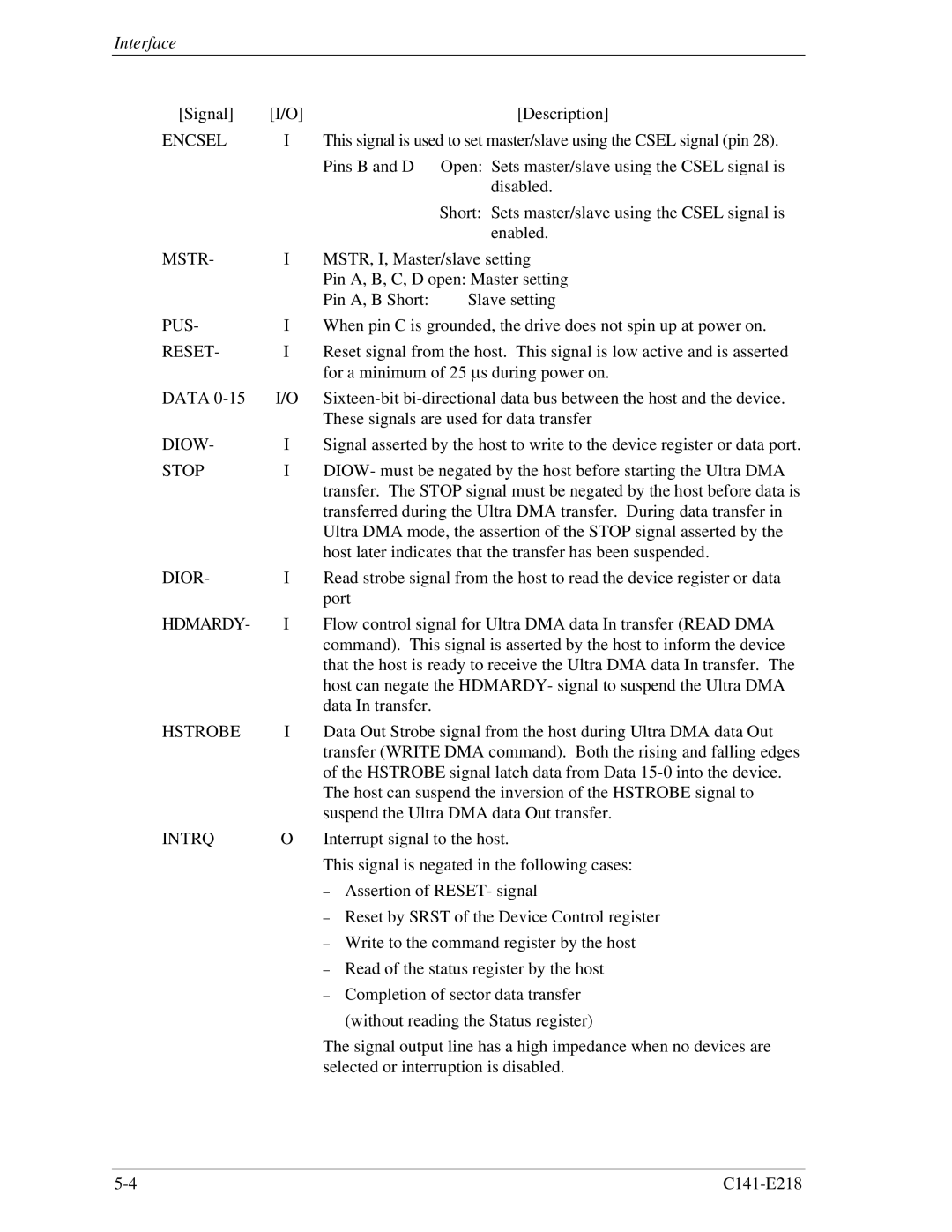

Interface

Interface signals

Physical Interface

Signal assignment on the connector

Signal assignment on the interface connector

DA1 PDIAG-, Cblid DA0 DA2

Dasp GND

Mstr

Diow

Stop

Dior

Pdiag

Cblid

Dasp

Iordy

Logical Interface

DA2 DA1 DA0

1 I/O registers

I/O registers

Command block registers

Error register X’1F1’

Data register X’1F0’

UNC Idnf

Sector Count register X’1F2’

Features register X’1F1’

SET Multiple Mode

Cylinder High register X’1F5’

Sector Number register X’1F3’

Cylinder Low register X’1F4’

Device/Head register X’1F6’

DEV HS3 HS2 HS1 HS0

Status register X’1F7’

BSY

Interface

Alternate Status register X’3F6’

Command register X’1F7’

Control block registers

Host Commands

Command code and parameters

Device Control register X’3F6’

HOB Srst

Command code and parameters 1

Parameter Used

Command code and parameters 2

EXT Write Multiple FUA EXT Flush Cache EXT

Host Commands

Command descriptions

Host Commands

Recalibrate X’10’ to X’1F’

Read Sectors X’20’ or X’21’

MSB

End head No. / LBA MSB

Write Sectors X’30’ or X’31’

1F7HST Status information 1F6HDH

Write Verify X’3C’

Read Verify Sectors X’40’ or X’41’

Seek X’70’ to X’7F’

Execute Device Diagnostic X’90’

Diagnostic code

Host Commands

Initialize Device Parameters X’91’

Download Microcode X’92’

Operation of Download Microcode

Standby Immediate X’94’ or X’E0’

Unload Feature Unload Immediate Command

Host Commands

Standby X’96’ or X’E2’

Idle X’97’ or X’E3’

Interface

Check Power Mode X’98’ or X’E5’

’FF’

Sleep X’99’ or X’E6’

Smart X’B0

Features register values subcommands and functions 1

Features register values subcommands and functions 2

Smart Enable Operations

Smart Disable Operations

Smart Read LOG

Smart Return Status

Features register values subcommands and functions 3

’DB’ Smart ENABLE/DISABLE Auto OFF-LINE

Host Commands

Format of insurance failure threshold value data

Format of device attribute value data

1FF

Data format version number

Attribute ID

Status Flag

Current attribute value

Attribute value for the worst case so far

Raw attribute value

11 Self-test execution status

10 Off-line data collection status

Self-test execution status

Off-line data collection capability

12 Off-line data collection capability

Failure prediction capability flag

13 Failure prediction capability flag

Error logging capability

14 Error logging capability

Check sum

Insurance failure threshold

Smart error logging

16 Data format of Smart Summary Error Log

Command data structure

Error data structure

Total number of drive errors

17 Data format of Smart Comprehensive Error Log

Smart self-test

18 Smart self-test log data format

1FC

Self-test number

19 Selective self-test log data structure

Test span

Current LBA under test

Current span under test

Selective self-test pending time min

Feature flags

20 Selective self-test feature flags

Device Configuration XB1

Device Configuration Restore

Device Configuration Freeze

Device Configuration Identify

Device Configuration Restore FR = C0h

Device Configuration Freeze Lock FR = C1h

Device Configuration Identify FR = C2h

Device Configuration SET FR = C3h

Interface

21 Device Configuration Identify data structure

Interface

Execution example of Read Multiple command

Read Multiple X’C4’

MSB

Write Multiple X’C5’

Interface

SET Multiple Mode X’C6’

Interface

Read DMA X’C8’ or X’C9’

End head No. / LBA MSB

Write DMA X’CA’ or X’CB’

Interface

Read Buffer X’E4’

Flush Cache X’E7’

Write Buffer X’E8’

Identify Device X’EC’

Identify Device DMA X’EE’

22 Information to be read by Identify Device command 1

’3FFF’

22 Information to be read by Identify Device command 2

Word

Command without interrupt supports 2, 4, 8 and 16 sectors

= Supports the Host Protected Area feature set

= Supports the CFA Compact Flash Association feature set

Interface

Host Commands

Interface

Host Commands

Word Bit Reserved Security level High, 1 Maximum

SET Features X’EF’

23 Features register values and settable modes

’BB’

’CC’

Data Transfer Mode

Advanced Power Management APM

Automatic Acoustic Management AAM

24 Contents of Security SET Password data

At command issuance I-O register contents 1F7hCM

Security UNLOCKX’F2’

When the master password is selected

When the user password is selected

Interface

Security Erase Prepare X’F3’

Security Erase Unit X’F4’

Security Freeze Lock X’F5’

At command issuance I-O register contents 1F7hCM

26 Contents of security password

Interface

Read Native MAX Address X’F8’

SET MAX X’F9’

SET MAX Address

SET MAX SET Password FR = 01h

SET MAX Lock FR = 02h

SET MAX Unlock FR = 03h

SET MAX Freeze Lock FR = 04h

Host Commands

Read Sectors EXT X’24’ Option customizing Description

Read DMA EXT X’25’ Option customizing Description

Error reporting conditions

Read Multiple EXT X’29’ Option customizing Description

Read LOG EXT X2F Optional command Customize Description

Host Commands

Write Sectors EXT X’34’ Option customizing Description

Write DMA EXT X’35’ Option customizing Description

SET MAX Address EXT X’37’ Option customizing Description

SET MAX LBA

Write Multiple EXT X’39’ Option customizing Description

Write DMA FUA EXT X’3D’ Option customizing Description

Write LOG EXT X’3F’ Optional command Customize Description

Host Commands

Read Verify Sectors EXT X’42 Option customizing Description

Write Multiple FUA EXT X’CE’ Option customizing Description

Flush Cache EXT X’EA’ Option customizing Description

Error posting

27 Command code and parameters 1

27 Command code and parameters 2

Execute Device Diagnostic Initialize Device Parameters

Command Protocol

PIO Data transferring commands from device to host

Read Sectors Command protocol

Protocol for command abort

PIO Data transferring commands from host to device

Write Sectors command protocol

Commands without data transfer

Other commands

DMA data transfer commands

Read Multiple EXT Write Multiple EXT/FUA EXT Sleep

Read DMA EXT Write DMA EXT/FUA EXT Indentify Device DMA

Normal DMA data transfer

Ultra DMA Feature Set

Overview

Initiating an Ultra DMA data in burst

Phases of operation

Ultra DMA data in commands

Pausing an Ultra DMA data in burst

Data in transfer

Terminating an Ultra DMA data in burst

Ultra DMA Feature Set

Interface

Ultra DMA data out commands

Initiating an Ultra DMA data out burst

Pausing an Ultra DMA data out burst

Data out transfer

Terminating an Ultra DMA data out burst

Interface

Ultra DMA CRC rules

Series termination required for Ultra DMA

28 Recommended series termination for Ultra DMA

DIOR-HDMARDY-HSTROBE

DIOW-STOP

PIO data transfer timing

Timing

PIO data transfer

10 Multiword DMA data transfer timing mode

Multiword data transfer

Ultra DMA data transfer

11 Initiating an Ultra DMA data in burst

Name Mode Comment

Strobe

29 Ultra DMA data burst timing requirements 2

MIN MAX

Mode Name Comment

30 Ultra DMA sender and recipient timing requirements

Sustained Ultra DMA data in burst

Dstrobe at device

DD150 at device Dstrobe at host

DD150 at host

Host pausing an Ultra DMA data in burst

Dmarq

Dmack

Hdmardy

Device terminating an Ultra DMA data in burst

Stop

DA0, DA1, DA2 CS0, CS1

Host terminating an Ultra DMA data in burst

Host

16 Initiating an Ultra DMA data out burst

Hstrobe at device DD150 at device

Sustained Ultra DMA data out burst

Hstrobe at host DD150 at host

Hstrobe host DD150 Host

Device pausing an Ultra DMA data out burst

Device DMACK- host Stop host DDMARDY- device

Host terminating an Ultra DMA data out burst

19 Host terminating an Ultra DMA data out burst

DD150 Host

Device terminating an Ultra DMA data out burst

Dmarq device DMACK- host

Only master device is present

Power-on and reset

Master and slave devices are present 2-drives configuration

Operations

Device Response to the Reset

Response to power-on

Response to hardware reset

Response to power-on

Response to hardware reset

Response to software reset

Response to software reset

Response to diagnostic command

Response to diagnostic command

Power Save

Power save mode

Active mode

Active idle mode

Standby mode

Sleep mode

Spare area

Power commands

Defect Processing

Track slip processing

Alternating processing for defective sectors

Sector slip processing

Automatic alternating processing

Automatic alternating processing

8MB buffer 8,388,608 bytes

Read-ahead Cache

Data buffer structure

Commands that are targets of caching

Caching operation

Data that is a target of caching

Invalidating caching-target data

Smart

Using the read segment buffer

Miss-hit

Sequential hit

Full hit

Partial hit

Command that are targets of caching

Write Cache

Cache operation

Invalidation of cached data

Status report in the event of an error

Reset response

Caching function when power supply is turned on

Enabling and disabling

Write Cache

This page is intentionally left blank

Glossary

Power save mode

Rotational delay

PIO Programmed input-output

Positioning

Status

VCM

This page is intentionally left blank

Acronyms and Abbreviations

This page is intentionally left blank

Index

AAM

Index

Host terminating ultra DMA data

Read Sectors Command

Read Native MAX Address

Surface temperature measurement

This page is intentionally left blank

Comment Form

Japan

This page is intentionally left blank

MHV2120AT, MHV2100AT, MHV2080AT, MHV2060AT, MHV2040AT

C141-E218-01EN

This page is intentionally left blank