GENE-8310

Intel Celeron M Processor Subcompact Board With LVDS, Ethernet

6 Channel Audio & Mini PCI

SubCompact Board

Copyright Notice

Acknowledgments

Packing List

Chapter 2 Quick Installation Guide

Contents

Chapter 1 General Information

Chapter 4 Driver Installation

Chapter 3 Award BIOS Setup

Appendix A Programming The Watchdog Timer

Appendix B

I/O Information

IRQ Mapping Chart

I/O Address Map

Chapter

General Information

Chapter 1 General Information 1

Superb Performance and Controllable Power Usage

1.1 Introduction

Multiple Display Modes

Chapter 1 General Information

Wide Expansion Capability

1.2 Features

48-bit Dual Channels LVDS TFT LCD 10/100Mbps Fast Ethernet

AC-97 3D Surround 5.1 Channel Audio

Supports Type II CompactFlash Memory

1.3 Specifications

System

Display

4 USB 2.0 Ports Does not

Two 5 x 2 Pin Headers Support

support Wake-up function

Chapter 2 Quick Installation Guide

Quick Installation Guide

Part No. 2007831011 Printed in Taiwan JAN

2.1 Safety Precautions

2.2 Location of Connectors and Jumpers Component Side

The Height of Cooling System Depends on Customer Cooling Device

Solder Side

CFD1 DIMM1

2.3 Mechanical Drawing

Component Side

The Height of Cooling System Depends on Customer Cooling Device

103.51

3.23 8.89 0.00 72.39 0.58 114.30

133.93

0.58

0.00

Jumpers

2.4 List of Jumpers

Label

Function

Connectors

2.5 List of Connectors

CN17

Open

2.6 Setting Jumpers

Closed

2.10 USB2.0 Port 1 Connector CN1

2.7 Clear CMOS Selection JP1

2.8 LCD Voltage Selection JP2

2.9 COM2 RI/+5V Selection JP5

2.11 USB2.0 Port 2 Connector CN2

2.12 Primary IDE Hard Drive Connector CN3

DIO Address is 801H

2.13 Digital IO Connector CN4

Name

2.15 Serial Port COM2 Connector CN6

2.14 Front Panel CN5

2.16 Parallel Port Connector CN7

2.18 4P Power Connector CN9

2.17 Dual Channel LVDS Connector CN8

PinSignal

2.20 DVI Connector CN11

2.19 TV-Out Connector CN10

2.21 Audio Input/Output Connector CN12

2.22 Ethernet 10/100Base-TX RJ-45 Phone Jack Connector CN13

2.23 External 5VSB/PWRGD Connector CN14

2.24 IrDA Connector CN15

G E N E - 8

2.26 Mini-DIN PS/2 Connector CN17

2.25 Fan Connector CN16

2.27 Serial Port COM1 Connector CN18

2.28 CRT Display Connector CN19

2.29 External Battery VBAT2

2.30 Mini PCI Slot MPCI1

2.31 CompactFlash Disk Slot CFD1

SubCompact Board

Award BIOS Setup

Chapter 3 Award BIOS Setup

System configuration verification

3.1 System Test and Initialization

Entering Setup

Standard CMOS Features

Advanced BIOS Features

Advanced Chipset Features

Power Management Setup

PnP/PCI Configurations

Load Fail-Safe Defaults

Load Optimized Defaults

Save and Exit Setup

Set Supervisor/User Password

Exit Without Saving

Driver Installation

Chapter 4 Driver Installation

Follow the sequence below to install the drivers

4.1 Installation

Chapter4 Drivers Installation

Step 4 - Install Realtek AC97 codec Driver

Appendix

Programming the Watchdog Timer

Appendix A Programming the Watchdog Timer A-1

A.1 Programming

Configuring Sequence Description

Appendix A Programming the Watchdog Timer A-2

2 Modify the Data of the Registers

1 Enter the MB PnP Mode

3 Exit the MB PnP Mode

WatchDog Timer Configuration Registers

Configure Control Index=02h

Appendix A Programming the Watchdog Timer A-4

WatchDog Timer Control Register Index=71h, Default=00h

WatchDog Timer Configuration Register Index=72h, Default=00h

WatchDog Timer Time-out Value Register Index=73h, Default=00h

Appendix A Programming the Watchdog Timer A-5

A.2 ITE8712 Watchdog Timer Initial Program

game port enable mov cl call SetLogicDevice InitialOK

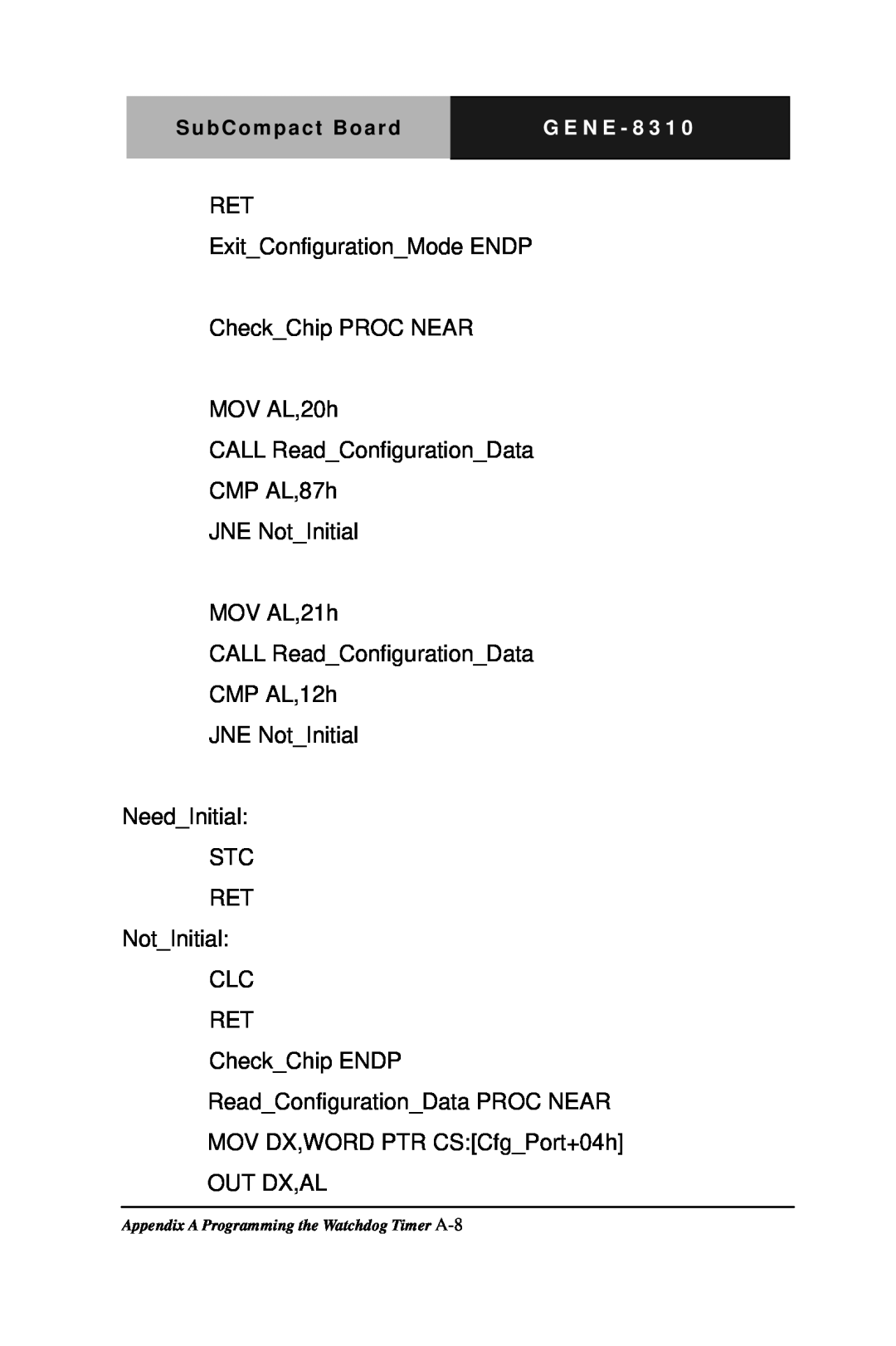

RET ExitConfigurationMode ENDP CheckChip PROC NEAR MOV AL,20h

CALL ReadConfigurationData CMP AL,87h JNE NotInitial MOV AL,21h

CALL ReadConfigurationData CMP AL,12h JNE NotInitial NeedInitial STC

RET NotInitial CLC RET CheckChip ENDP ReadConfigurationData PROC NEAR

MOV DX,WORD PTR CSCfgPort+06h IN AL,DX RET ReadConfigurationData ENDP

END Main

Appendix A Programming the Watchdog Timer A-10

SetLogicDevice proc near push ax push cx xchg al,cl mov cl,07h

call SuperioSetReg pop cx pop ax ret SetLogicDevice endp

I/O Information

Appendix B I/O Information B-1

B.2 1st MB Memory Address Map

B.1 I/O Address Map

Appendix B I/O Information B-2

B.4 DMA Channel Assignments

B.3 IRQ Mapping Chart

Appendix B I/O Informaion B-3