8355

Contents

8355 N/B Maintenance

Trouble Shooting ………………………………………………………………………………………

Audio Failure ………….……………………………………………………………………………………………

Introduction

Hardware Engineering Specification

8355 N/B Maintenance

CPU

System Hardware Part

Compatible with Existing 32-bit Code Base

CPU ClawHammer Processor

AMD x86-64 Technology

Integrated Memory Controller

HyperTransport. Technology to I/O Devices

Power Management

Kbyte 2-way Associative ECC-Protected L1 Data Cache

Way Associative ECC-Protected L2 Cache

Packaging

Power Supplies

Electrical Interfaces

System frequency synthesizerICS950402

System frequency

Programmable Timing Control Hub AMD-K8 processor

Recommended Application

Features

High Performance K8 CPU Interface

VIA K8T800+VT8235

3.1 K8T800

Full Featured Accelerated Graphics Port AGP 8x Controller

8355 N/B Maintenance

3.2 VT8235

8355 N/B Maintenance

Smartshader Advanced Shader Technology

General Description

Dual Display Support

High Performance Memory Support

Ideal for Windows 2000 and Windows XP

General and Interfacing Features

8355 N/B Maintenance

8355 N/B Maintenance

5 AC’97 Audio System C-MEDIA Electronics INC., CMI9738-S

8355 N/B Maintenance

MDC PCTel Modem Daughter Card PCT2303W

Compatibility

Operating System Compatibility

Modulation

Dtmf signal level

Error Correction

Data Compression

DTE interface Dtmf Tone Frequency

High group 10+/-2dBm Low group 12+/-2dBm

Transmit Level

Integrated 400 Mbit 2-Port PHY

7 VT6307L PCI 1394a Integrated Host Controller

Overview

8355 N/B Maintenance

Embedded CONTROLLER-H8

Main Features

Interface

Timer

Memory

Ports

Converter

Other features

Power-down modes

Interrupts

Wait control

Features

64MB, 128MB, 256MB, 512MB x64 200-Pin DDR Sdram SODIMMs

System Flash Memory Bios

Memory System

11 VT6103 Fast Ethernet 10/100 1-PORT PHY/TRANSCEIVER

3V operation with 5V tolerant

Cardbus/MediaReader Controller

Smart Card Interface

Pin Lqfp / 209-ball Lfbga package for CB710 PCI Interface

CardBus Interface

Memory Stick Interface

Secure Digital Interface

Power Management Control Logic

Interrupt configuration

Stick interface

SmartMedia Interface

Misc Control Logic

Supports Zoomed Video port Power Switch Interface

General Description

Outstanding Features

SuperI/O-PC87393

8355 N/B Maintenance

Hot Key Function

Keys Feature Meaning Combination

Other Functions

Cover Switch

Power ON/OFF/Suspend/Resume Button

APM mode

Acpi mode

Fan power on/off management

LED Indicators

7 I/O Port

Cmos Battery

Mini PCI type III BBattery current limit and learning

ROM Drive

Peripheral Components

System Management Mode

Power Management

Full on mode

Doze Mode

Suspend to HDD

Suspend to Dram

HDD & Video Access

Other Power Management Functions

Appendix 1 VT 8235 Gpio Definition

To the previous table

Shadowed block is the selected function

Appendix 2 H8 Pins Definition

Charging

KB OUT8

Ilimit

↑ Pull High ↓ Pull Low →3V Level shift

CPU

Appendix 3 8355 product spec

AC adapter

FCC, CE, UL, TUV, CB, Bsmi

System View

System View and Disassembly

Front View

Left-side View

Rear View

Right-side View

Top View

Bottom View

System Disassembly

DDR Sdram

Reassembly

Battery Pack

Disassembly

Remove three screws

Keyboard

Slide out the keyboard cover

Disconnect the cable from system board. Figure

Remove four screws

3 CPU

Disconnect the fan’s cord

11 Remove HDD compartment

HDD Module

13 slide out the hard disk drive

15 Remove the CD/DVD -ROM drive

5 CD/DVD-ROM Drive

16 Remove the SO-DIMM

SO-DIMM

17 Remove two screws

LCD Assembly

19 Remove the hinge cover

21 Remove the LCD assembly

22 Unscrew four screws

Inverter Board

8355 N/B Maintenance

24 Separate the LCD panel

LCD Panel

8355 N/B Maintenance

26 Unscrew nine screws

System Board

28 Remove the top cover

Unscrew one screw and disconnect fan’s cord. Figure

Reassembly

32 Remove the modem card

Modem Card

33 Free the touch pad

Touch Pad

8355 N/B Maintenance

Main Board Side a

Definition & Location of Connectors / Switches

VR1 Volume Controller

Definition & Location of Connectors/ Switches

Main Board Side B

Definition & Location of Major Components

U517 TPA0202 Audio Amplifier U518 CMI9738 Audio Codec

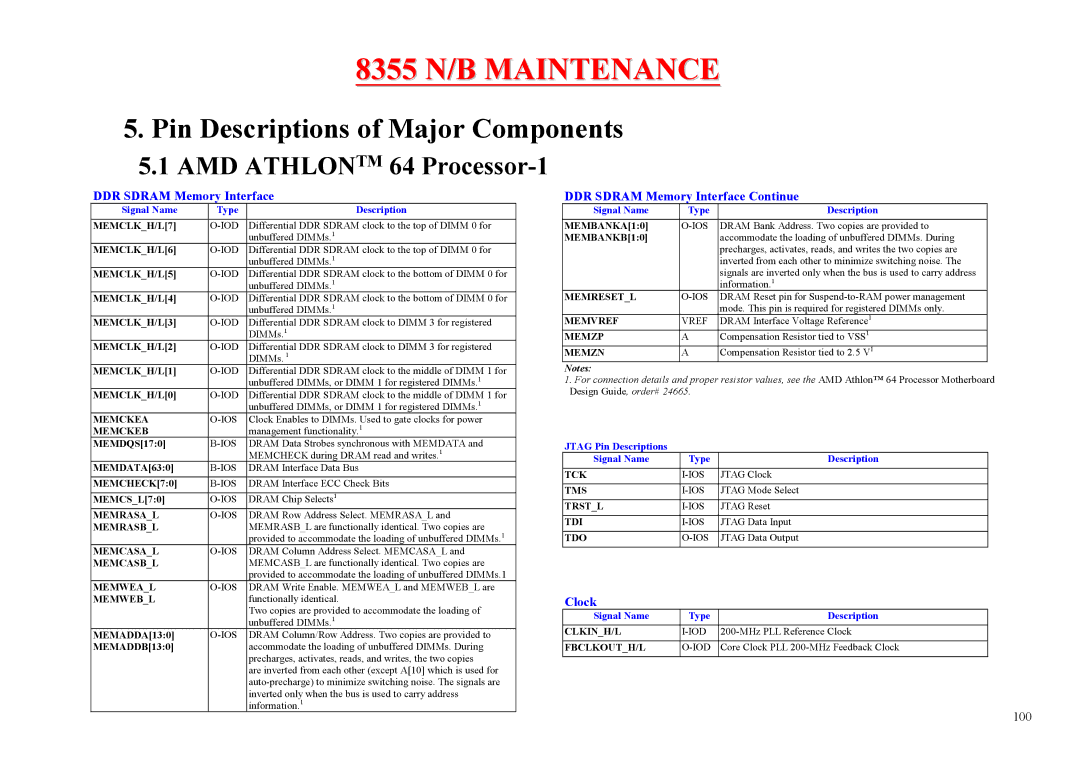

AMD Athlontm 64 Processor-1

Pin Descriptions of Major Components

DDR Sdram Memory Interface

DDR Sdram Memory Interface Continue

HyperTransport Technology

AMD Athlontm 64 Processor-2

Debug

Miscellaneous

Hyper Transport Receive Interface

K8T800MVT8385 North Bridge-1

Hyper Transport transmit Interface

Hyper Transport Control

K8T800MVT8385 North Bridge-2

Link Interface

AGP Bus Interface

Girdy GIRDY#

K8T800MVT8385 North Bridge-3

K8T800MVT8385 North Bridge-4

Clock, Reset, Power Control and Test

Straps

VT8235 South Bridge-1

Advanced Programmable Interrupt Controller APICInterface

CPU Speed Control Interface

VT8235 South Bridge-2

Low Pin Count LPCInterface

CPU Interface

PCI Bus Interface Continue

VT8235 South Bridge-3

PCI Bus Interface

LAN Controller -Media Independent Interface MII

VT8235 South Bridge-4

General Purpose I/O

Universal Serial Bus 2.0 Interface

UltraDMA-133 /100 /66 /33 Enhanced IDE Interface

VT8235 South Bridge-5

UltraDMA-133 /100 /66 /33 Enhanced IDE Interface Continue

Serial IRQ

VT8235 South Bridge-6

Resets,Clocks,and Power Status

General Purpose Inputs

General Purpose Inputs Continue

VT8235 South Bridge-7

Power Management and Event Detection

Power Management and Event Detection Continue

VT8235 South Bridge-8

Power and Ground

Internal Keyboard Controller

AC97 Audio /Modem Interface

ISA Subset /Parallel Bios ROM Interface

Power and Ground Continue

VT8235 South Bridge-9

System Management Bus SMBInterface I 2 CBus

U506

System Block Diagram

U503

Maintenance Diagnostics

Code Post Routine Description

Error Codes

118

Debug Tool

Diagnostic Tool for Mini PCI Slot

Diagnostic Tool for PIO Port

Trouble Shooting

+1.25VSREFMEM

No Power

+1.2VLDTA Agpvddq

PJ502

No power

Adinp

Battery Can not Be Charged

Battery can not Charge

System Clock Check

No Display

No Display System Failure

Reset Circuit Checking1

No Display System Failure

Reset Circuit Checking2

No Display

Parts Signals

U9 P6

AGP Controller Failure LCD No Display

Charge BD J2,J3 are cold colder?

AGP Controller Failure

J503

External Monitor No Display

Display Yes OK? Replace faulty monitor

Symptom The extend DDR RAM is failure or system hangs up

Memory Test Error

Parts

Memory Test Error

Key Board Controller

Keyboard K/B Touch-Pad T/P Test Error

Test Yes Ok? Replace the faulty Keyboard or Touch-Pad

Keyboard or Touch-Pad Test Error

Hard Disk Driver Test Error

Hard Driver Test Error

Hard Disk Driver Test Error

J530

CD-ROM Driver Test Error

CD-ROM Driver Test Error

Symptom An error occurs when a USB I/O device is installed

USB Test Error

U501

PartsSignals

USB Test Error

PC-Card Socket Failure

Symptom An error occurs when a PC card device is installed

PC Card Test Error

Memory-Card Socket Failure

Memory-Card Socket Failure

Memory Card Test Error

Symptom An error occurs when IEEE1394 device is installed

IEEE1394 Test Error

Test Error

Symptom An error occurs when LAN device is installed

LAN Test Error

Correct it

LAN Test Error

Input Of Audio Subsystem

Audio Failure

Output Of Audio Subsystem

Audio Drive Failure

Part Number Description LocationS

Spare Part List-1

Spare Part List-2

CFM-BATFUSE Thermal 98C

Spare Part List-3

DIODEBAV70LT1,70V,225MW,SOT-23

Spare Part List-4

DVD Combo DRIVE8X24X10X24X,SBW

Spare Part List-5

ICEM6A9320BI-3.6M,DDR SDRAM,4MX

Spare Part List-6

ICVT8235,SOUTH BRIDGE,BGA,487P

Spare Part List-7

Spare Part List-8

LABELSOFTWARE,INSYDE BIOS-M

RELAYREED,200V,.5A,NORMAL Open SW1

Spare Part List-9

RES2M

Spare Part List-10

RP7,RP8

Spare Part List-11

RP6,RP9

Spare Part List-12

TRANSDTC144WK,NPN,SOT-23,SMT

Spare Part List-13

Spare Part List-14

WIRE#28,UL1061,40MM,BLUE,PRC

Page

Page

Model

Memresetl

CPURESET# CPURESET# 3,12 DDRRASB#

CPURESET#

Corefbh

VID0

NBLDTRST# CPURESET#

VID1

VID2

DIMM-SLOT & Termination

K8T400M- VT8385

H8RESET#

FS0 14MSBIOSC

ACPOWER#

H8RESET# BATTG#

M10GPIO0

AGPRESET#

M10GPIO4

M10GPIO5

ATI M10-P2/4

MEMAMA2

MEMAMD2

MEMAMD0

VMDA0 MEMAMD0

VMDA0 VMA0

VMA0

VMB0 VMDB0 VMDB32 VMA1 VMDA1 VMDA33

VMA2

Crtgreen

Crtin

+PANELVDD

PANELID0 PANELID2 PANELID3

VT8235 1/3- PCI & USB

VT8235 2/3- IDE & AC97

VT8235 3/3- VLINK&LAN

IDEDPDD1 HDPDD2

IDEDPDD0

IDEDPDD2

HDPDD3 IDEDPDD3 HDPDD4

POWERONRESET#

CAD11 CVS1 CARDRESET#

CAD1

CAD2

Wirelesspd

MINIPCIGPORESET#

SDCD# GND SDWP#

SDWP# SDDATA1 LEDCL190 SDDATA0 Sdclk Sdcmd SDDATA3 SDDATA2

TPA0N

PCIAD4 PCIAD1

TPA0P

TPB0P

LANMRXDV2

LANPHYRESET#

PJTX+

LANTX+

Micint

Avdd Micvref

Micext AC97SDOUT

AC97SDIND0

DEVICEDECT#

Audiomute Ampmute

DECTHP#/OPT

Spdifout

LPCSPIORESET# LPCFRAME#

LPCSPIORESET# PD6

INIT#

PIOD/INT#

SCI#/FANSWITCH H8WAKEUP#

Tclkd H8RESET#

H8ENABKL H8RESET#

SCI#/FANSWITCH

USBOC5# USBOC2#

USBOC0# USBOC2#

USBP0P

USBP2P

SD2 SA2 PCIGNT#4 SD3 SA3 PCIGNT#5 PCICARDBUSGNT#0

SA0 SD1 SA1

SD4 SA4

SD6 SA6

OD5

OD3

Pgvcccore

PWRONM9

+2.5VS&+1.25VS&+1.8V&+1.2V

DVMAINP2

+3VS / +5VS

VOSENSE1

VOSENSE2

For M10 +1.2V&+1.0V

ADP1

Adinp

Batt

Ilimit

Liovp

Adinp Batt

Liovp Charging

Battdead

PVID0

VMAINP3

PVID1

PVID2

Reference Material

Tel Fax Second Edition Nov Mail Willy .Chen @ mic.com.tw