8355 N/B MAINTENANCE

5.2 K8T800M(VT8385) North Bridge-3

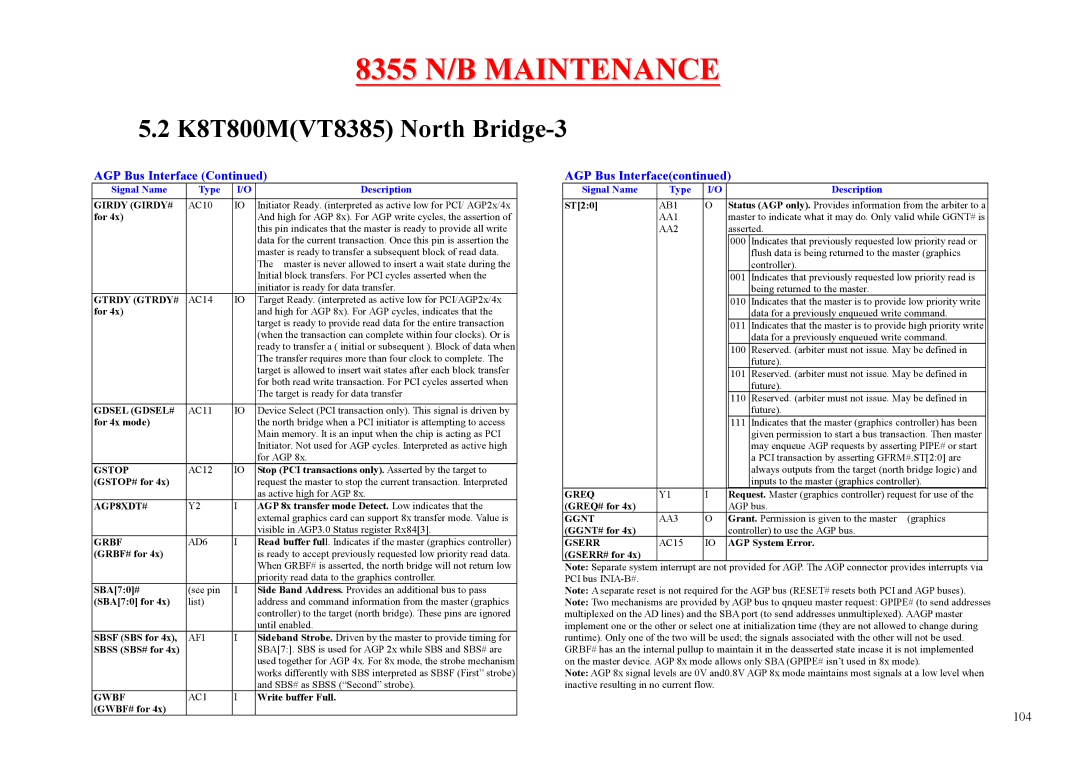

AGP Bus Interface (Continued)

Signal Name | Type | I/O | Description |

GIRDY (GIRDY# | AC10 | IO | Initiator Ready. (interpreted as active low for PCI/ AGP2x/4x |

for 4x) |

|

| And high for AGP 8x). For AGP write cycles, the assertion of |

|

|

| this pin indicates that the master is ready to provide all write |

|

|

| data for the current transaction. Once this pin is assertion the |

|

|

| master is ready to transfer a subsequent block of read data. |

|

|

| The master is never allowed to insert a wait state during the |

|

|

| Initial block transfers. For PCI cycles asserted when the |

|

|

| initiator is ready for data transfer. |

GTRDY (GTRDY# | AC14 | IO | Target Ready. (interpreted as active low for PCI/AGP2x/4x |

for 4x) |

|

| and high for AGP 8x). For AGP cycles, indicates that the |

|

|

| target is ready to provide read data for the entire transaction |

|

|

| (when the transaction can complete within four clocks). Or is |

|

|

| ready to transfer a ( initial or subsequent ). Block of data when |

|

|

| The transfer requires more than four clock to complete. The |

|

|

| target is allowed to insert wait states after each block transfer |

|

|

| for both read write transaction. For PCI cycles asserted when |

|

|

| The target is ready for data transfer |

|

|

|

|

GDSEL (GDSEL# | AC11 | IO | Device Select (PCI transaction only). This signal is driven by |

for 4x mode) |

|

| the north bridge when a PCI initiator is attempting to access |

|

|

| Main memory. It is an input when the chip is acting as PCI |

|

|

| Initiator. Not used for AGP cycles. Interpreted as active high |

|

|

| for AGP 8x. |

GSTOP | AC12 | IO | Stop (PCI transactions only). Asserted by the target to |

(GSTOP# for 4x) |

|

| request the master to stop the current transaction. Interpreted |

|

|

| as active high for AGP 8x. |

AGP8XDT# | Y2 | I | AGP 8x transfer mode Detect. Low indicates that the |

|

|

| extemal graphics card can support 8x transfer mode. Value is |

|

|

| visible in AGP3.0 Status register Rx84[3]. |

GRBF | AD6 | I | Read buffer full. Indicates if the master (graphics controller) |

(GRBF# for 4x) |

|

| is ready to accept previously requested low priority read data. |

|

|

| When GRBF# is asserted, the north bridge will not return low |

|

|

| priority read data to the graphics controller. |

SBA[7:0]# | (see pin | I | Side Band Address. Provides an additional bus to pass |

(SBA[7:0] for 4x) | list) |

| address and command information from the master (graphics |

|

|

| controller) to the target (north bridge). These pins are ignored |

|

|

| until enabled. |

SBSF (SBS for 4x), | AF1 | I | Sideband Strobe. Driven by the master to provide timing for |

SBSS (SBS# for 4x) |

|

| SBA[7:]. SBS is used for AGP 2x while SBS and SBS# are |

|

|

| used together for AGP 4x. For 8x mode, the strobe mechanism |

|

|

| works differently with SBS interpreted as SBSF (First” strobe) |

|

|

| and SBS# as SBSS (“Second” strobe). |

GWBF | AC1 | I | Write buffer Full. |

(GWBF# for 4x) |

|

|

|

AGP Bus Interface(continued)

Signal Name | Type | I/O |

| Description |

ST[2:0] | AB1 | O | Status (AGP only). Provides information from the arbiter to a | |

| AA1 |

| master to indicate what it may do. Only valid while GGNT# is | |

| AA2 |

| asserted. | |

|

|

| 000 | Indicates that previously requested low priority read or |

|

|

|

| flush data is being returned to the master (graphics |

|

|

|

| controller). |

|

|

| 001 | Indicates that previously requested low priority read is |

|

|

|

| being returned to the master. |

|

|

| 010 | Indicates that the master is to provide low priority write |

|

|

|

| data for a previously enqueued write command. |

|

|

| 011 | Indicates that the master is to provide high priority write |

|

|

|

| data for a previously enqueued write command. |

|

|

| 100 | Reserved. (arbiter must not issue. May be defined in |

|

|

|

| future). |

|

|

| 101 | Reserved. (arbiter must not issue. May be defined in |

|

|

|

| future). |

|

|

| 110 | Reserved. (arbiter must not issue. May be defined in |

|

|

|

| future). |

|

|

| 111 | Indicates that the master (graphics controller) has been |

|

|

|

| given permission to start a bus transaction. Then master |

|

|

|

| may enqueue AGP requests by asserting PIPE# or start |

|

|

|

| a PCI transaction by asserting GFRM#.ST[2:0] are |

|

|

|

| always outputs from the target (north bridge logic) and |

|

|

|

| inputs to the master (graphics controller). |

GREQ | Y1 | I | Request. Master (graphics controller) request for use of the | |

(GREQ# for 4x) |

|

| AGP bus. | |

GGNT | AA3 | O | Grant. Permission is given to the master (graphics | |

(GGNT# for 4x) |

|

| controller) to use the AGP bus. | |

GSERR | AC15 | IO | AGP System Error. | |

(GSERR# for 4x) |

|

|

|

|

Note: Separate system interrupt are not provided for AGP. The AGP connector provides interrupts via PCI bus

Note: A separate reset is not required for the AGP bus (RESET# resets both PCI and AGP buses).

Note: Two mechanisms are provided by AGP bus to qnqueu master request: GPIPE# (to send addresses multiplexed on the AD lines) and the SBA port (to send addresses unmultiplexed). AAGP master implement one or the other or select one at initialization time (they are not allowed to change during runtime). Only one of the two will be used; the signals associated with the other will not be used. GRBF# has an the internal pullup to maintain it in the deasserted state incase it is not implemented on the master device. AGP 8x mode allows only SBA (GPIPE# isn’t used in 8x mode).

Note: AGP 8x signal levels are 0V and0.8V AGP 8x mode maintains most signals at a low level when inactive resulting in no current flow.

104