HT 1000, JT 1000, MT 2000, MTS 2000, and MTX Series

Page

Safety

Foreword

Contents

Disassembly and Reassembly

Iii

Page

Replacement Parts Ordering

List of Tables

Related Publications Available Separately

Vii

Model Numbering System

Viii

Model Charts Model Programming Flashing, and Cloning

Model Chart

Conventional Systems Radios HT 1000 Models

Conventional Systems Radios JT 1000 and MT 2000 Models

H01RDH9PA3AN

Private Systems Radios MTS 2000 Models

PMUF6500D

A a

Xii

List of Antennas

List of Batteries

Maintenance Specifications for VHF Radios

Xiii

Maintenance Specifications for 800MHz Radios

Xiv

Glossary

ALC

PLL

Xvi

Introduction

R N I N G

Page

Recommended Test Equipment

Recommended Test Equipment

Service Aids and Recommended Tools

Field Programming

Service Aids

Motorola Part no Description Application

Service Tools

Recommended Service Tools

General Setup

Test Mode

Equipment Initial Control Settings

Earlier. If the radio is placed in Test Mode

Test Environments, HT 1000/JT 1000 Radios

NO. Description Function Beeps

Control Head Test Mode, HT 1000/JT 1000 Radios

Test Frequencies, HT 1000 / JT

Page

Page

Test Environments, MT 2000, MTS 2000, and MTX Series Radios

Test Frequencies, MT 2000, MTS 2000, and MTX Series Radios

Receiver Performance Checks

Test Name Communications Radio Test SET Comments Analyzer

Transmitter Performance Checks

Test Communications Radio Test SET Comments Name Analyzer

Power-up Display Codes

Error-Code Displays

Power-up Display Codes

Operational Display Codes

Operational Display Codes

Radio Alignment Procedure

General

Dtmf

Perform the following procedures in the sequence indicated

Reference Oscillator Alignment

Standard Test Modulation 1 kHz Tone

Front-End Pre-Selector VHF/UHF only

Rated Audio

Transmitter Power

Squelch

Transmit Power Setting

VHF UHF

Transmit Deviation Limit

Transmit Deviation Limit

Transceiver Board Identification

Transmit Deviation Limit Reference

Page

TX VCO Crossover Procedure

Dtmf Tuning High Speed Signalling

Signalling Deviation

RX VCO Crossover Procedure

Signalling Deviation

MDC

Disassembly and Reassembly

This Radio Contains STATIC-SENSITIVE

Disassembly to Board Level

Removing the Battery

Separating the Cover From the Chassis

Rotating the Front Cover

Separating Control Top From the Chassis

Disassembly of Control Top

Removing the RF and Controller Boards

Disassembly of Front Cover Assembly

Reassembly

Removing the Keypad/Display Board

Reinstalling the Speaker RetainerMAEPFBracket-22578-A

Page

Front Cover Assembly to Chassis

Seating the Flex

Knobs, Antenna, and Battery

Maintenance

Preventive Maintenance

Inspection Cleaning

Introduction

Safe Handling of Cmos Devices

General

Specific

If neighboring Pbga components are heated

Above 365 degrees F degrees C., they will

Suffer die-bond delamination and possible

Solder Tabs

Page

U t i o n

Thin Small Outline Package Tsop Components

To Replace an Pbga compo- nent

Removing and Replacing

Shields

To Remove the RF PA

To Replace the RF PA

Page

Exploded Views

Refer to electrical parts list transceiver board

Top-Display Radios

Keypad Radios

Uni-board Radios

SHIELD, PA

Page

Transceiver Controller Schematic and Circuit Board Notes

Circuit Board Layers

Integrated Circuit Details with Pin-Out Names

SYN

35U50 X Wlyww

Wlyww

Universal Connector Pin Numbers and Signal Assignments

Universal Connector Option Select OPT SEL Definition

MAEPF-2

CAPACITOR, Fixed pF ± 5%

Unless stated

Diode See Note

Fuse 1-Amp

U102

Error Feedback

NC NC NC NC CLK

5VREG SB+

BATT+

MAEPF-2630

CAPACITOR, Fixed pF ±30%

Transistor See Note

RESISTOR, Fixed Ω ± 5%

0625W unless stated

Switch

Connector EXT. ANT

These Levels Measured by Removing R52

DAC CLK

NC NC NC NC NC CLK

DET VDD VDD2

Cext

Batt

MAEPF-2630

COIL, RF nH

CAPACITOR, Fixed pF ± 25%

50V unless stated

RF Switch

CR6 CR7 CR8 CR9

ABP GND1 GND2 GND3 AG2

GND1 GND2 GND3 GND4 GND5

VDD VDD2

DET

NC3 NC4 NC5 NC6 NC7 NC8 NC9

VMULT2 Frefout

MAEPF-26305

3Pack.xls CAPACITOR, Fixed pF ± 5% Sheet Unless stated

RESISTOR, Fixed Ω ± 0.0625W

U105 U104

5VREG LCK

VCO MOD RAW B+

LCK SW B+

SYN SEL

Transceiver Board Parts List and Component Location Diagrams

CAPACITOR, Fixed pF ±5%

Fuse 1.0A Filter See Note 2, 73.35MHZ

RESISTOR, FixedΩ ± 5% .0625W unless stated

DIODE, Zener See Note 1

U101

CLK Batt

GND32

GND31

GND30

NUF6499B/C and NUF6502B/C 900MHz

Diode

U105

SYN SYN SEL

GND30 REF OSC

GND27

GND21

NUF/PMUF6499D 900MHz

Electrical Parts List, Transceiver 900MHz NUF/PMUF6499D

Reset 5V TX 0V RX

ANODE2 Pacntl INT CAP Antswbs Switch

GND GND1 GND2 RF Switch

To Universal Connector

Synthesizer

Je di HT/JT Tra ns .

DIODE, Zener

HearClear Option

U701

Hear

Clear

Resetb

U702

U708

Asficsel

SB+ Intspkr Error

Intmic Optenable Spkrcom

Spkrcom Aupaen Extspkr

Volsense NC3 Extspkrsel

NC5 NC6 NC7 NC8

U709

U706

Controller BOARD’ Parts List and Component Location Diagram

RESISTOR, Fixed Ω ± 5%

Chact Reset

GND10 GND11 GND12 GND13 Gnda

GND VEE

Upclk A3 Clke VDD3 VDD4

Vccence Enoe Enwe

Busy

Power Section

Analog Section SCK

SPI TX Data Mosi

SPI RX Data Miso

Main Power Switch

Vdd Regulator

Vaud Regulator

U712

MAEPF-25672

DIODE, Zener See Note

103

CAPACITOR, Fixed pF ±

Hiclmpen Compen Lcdis Hcidis Ffen

Sqdet Chact Univio Pwrrst Sqdet Chact

Icenab Ffout

Cpnenab Expout Ffenab Cbufou

UV2CS Bootstrp

VSS4 VSS1 Synsel Roscsel Ascficsel Bootstrp Csgen

Scirx Eecs Muxcntl SEL LED

Uvcs

SWB+ GND1 Blcntl Intspkr Reset Spkrcom Intmic

OPTB+/BOOTSEL Mosi

GND2 Keyint OPTSEL1

Extspkr Datalatch Extmic

NTN7512D/E, NTN7513E, NTN7857D/E and NTN7858D/E 107

MAEPF-26096

109

HearClear Components Not Placed on NCN6176A

CAPACITOR, Fixed pF ± 5% 50V unless stated

RESISTOR, Fixed Ω ± 0.0625W unless stated

SWB+ Sqdet Chact

Expin Lodsab Cbufin Expbyp Rssiin

Ffin VAG Nfilin

Ffcnt L

U705

Digital Section

Main Power Switch Vdd Regulator

U702

Front Cover Display Flex

Replacement Parts Ordering

Motorola Online

Mail Orders

115

Telephone Orders

FAX Orders

Parts Identification

116

Appendix a

Appendix a

Introduction Circuit Description

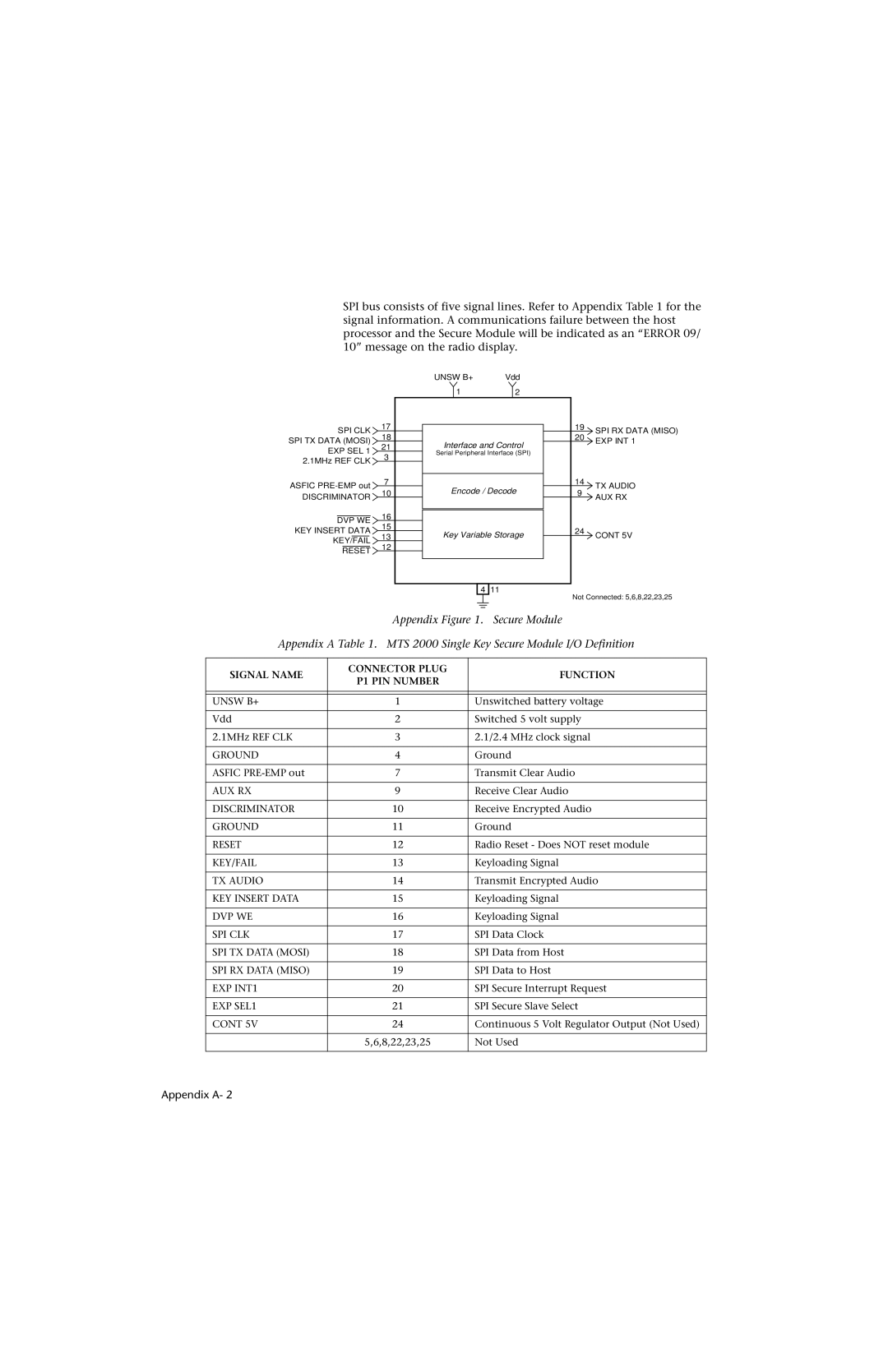

Signal Name Connector Plug Function P1 PIN Number

Appendix . Secure Module

Troubleshooting Secure Operations

Service Aid Retrofit Instructions

Appendix a . Key Variable Loader

Anti-static precautions must be observed at all times

General

Set Secure-Equipped Field

Set XL IC Present Field

Secure Alignment Procedure

Enable Secure On Desired

Secure Retrofit Tuning

Channels

Compensation

Appendix a . Secure Deviation

Removal And Installation

Removal

Appendix . Secure Module Location Detail

Appendix a . RSS Secure Parameters

XL&XL

Appendix B

Appendix B

Appendix B . HT 1000 Models

H01RDC9AA1BN

Appendix B . JT 1000 Models

Appendix B . MT 2000 Models

PMUE7272B PMCN6147B

H01SDH9AA7AN

Appendix B . MTS 2000 Models

H01RDD9PW1AN

H01RDH9PW1AN

H01SDH9PW1AN

H01UCH6PW1AN

PMUF6499D Pmcn

Appendix B . MTX Series Models

H01KDF9DB5AN

H01RDD9DB4AN

H01RDH9DB7AN

H01SDH9DB7AN

H01UCC6DF3AN

H01WCC4DB3AN

H01WCH4DB7AN

Page

Motorola, Inc West Sunrise Boulevard Ft. Lauderdale, FL