HPC167064 UART

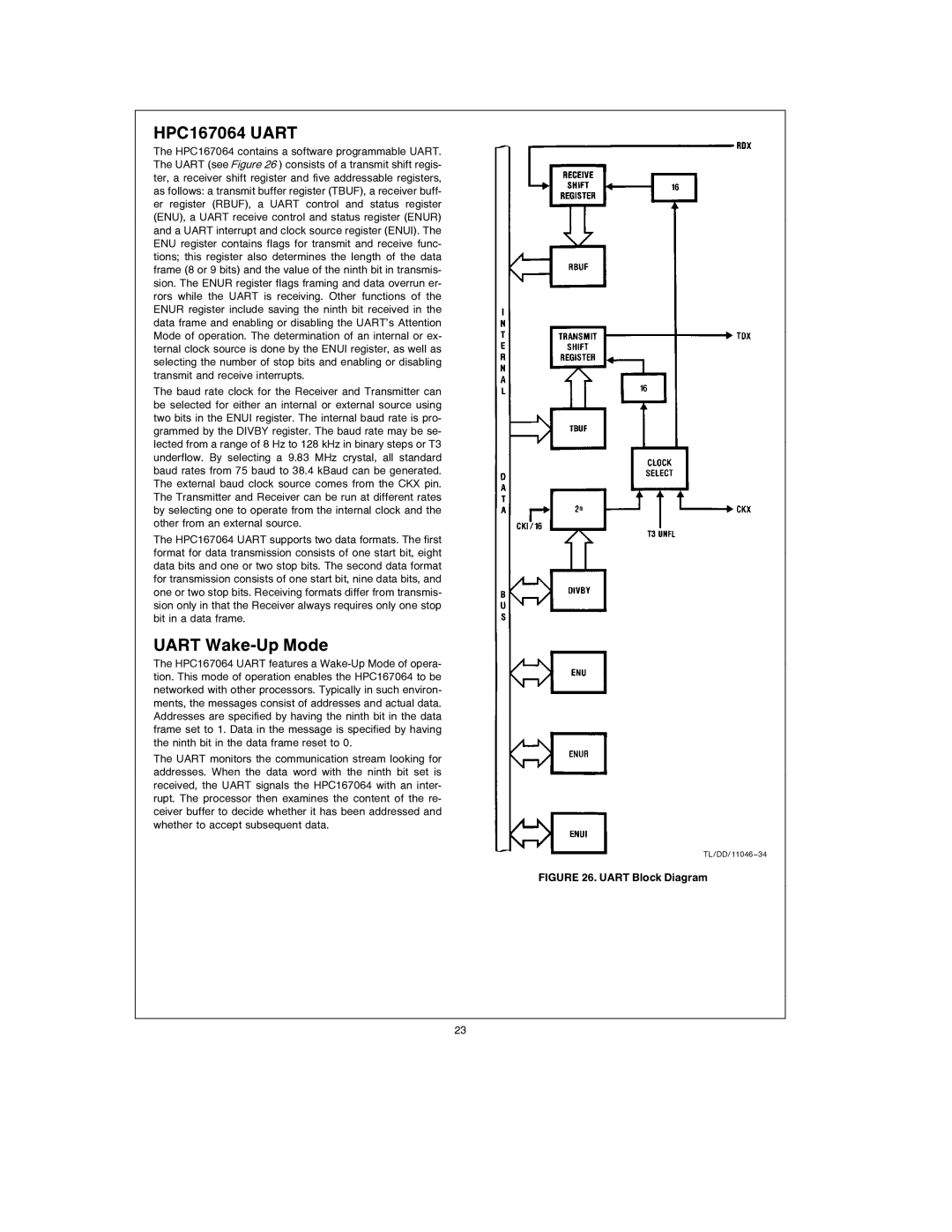

The HPC167064 contains a software programmable UART. The UART (see Figure 26 ) consists of a transmit shift regis- ter, a receiver shift register and five addressable registers, as follows: a transmit buffer register (TBUF), a receiver buff- er register (RBUF), a UART control and status register (ENU), a UART receive control and status register (ENUR) and a UART interrupt and clock source register (ENUI). The ENU register contains flags for transmit and receive func- tions; this register also determines the length of the data frame (8 or 9 bits) and the value of the ninth bit in transmis- sion. The ENUR register flags framing and data overrun er- rors while the UART is receiving. Other functions of the ENUR register include saving the ninth bit received in the data frame and enabling or disabling the UART’s Attention Mode of operation. The determination of an internal or ex- ternal clock source is done by the ENUI register, as well as selecting the number of stop bits and enabling or disabling transmit and receive interrupts.

The baud rate clock for the Receiver and Transmitter can be selected for either an internal or external source using two bits in the ENUI register. The internal baud rate is pro- grammed by the DIVBY register. The baud rate may be se- lected from a range of 8 Hz to 128 kHz in binary steps or T3 underflow. By selecting a 9.83 MHz crystal, all standard baud rates from 75 baud to 38.4 kBaud can be generated. The external baud clock source comes from the CKX pin. The Transmitter and Receiver can be run at different rates by selecting one to operate from the internal clock and the other from an external source.

The HPC167064 UART supports two data formats. The first format for data transmission consists of one start bit, eight data bits and one or two stop bits. The second data format for transmission consists of one start bit, nine data bits, and one or two stop bits. Receiving formats differ from transmis- sion only in that the Receiver always requires only one stop bit in a data frame.

UART Wake-Up Mode

The HPC167064 UART features a

The UART monitors the communication stream looking for addresses. When the data word with the ninth bit set is received, the UART signals the HPC167064 with an inter- rupt. The processor then examines the content of the re- ceiver buffer to decide whether it has been addressed and whether to accept subsequent data.

TL/DD/11046 – 34

FIGURE 26. UART Block Diagram

23