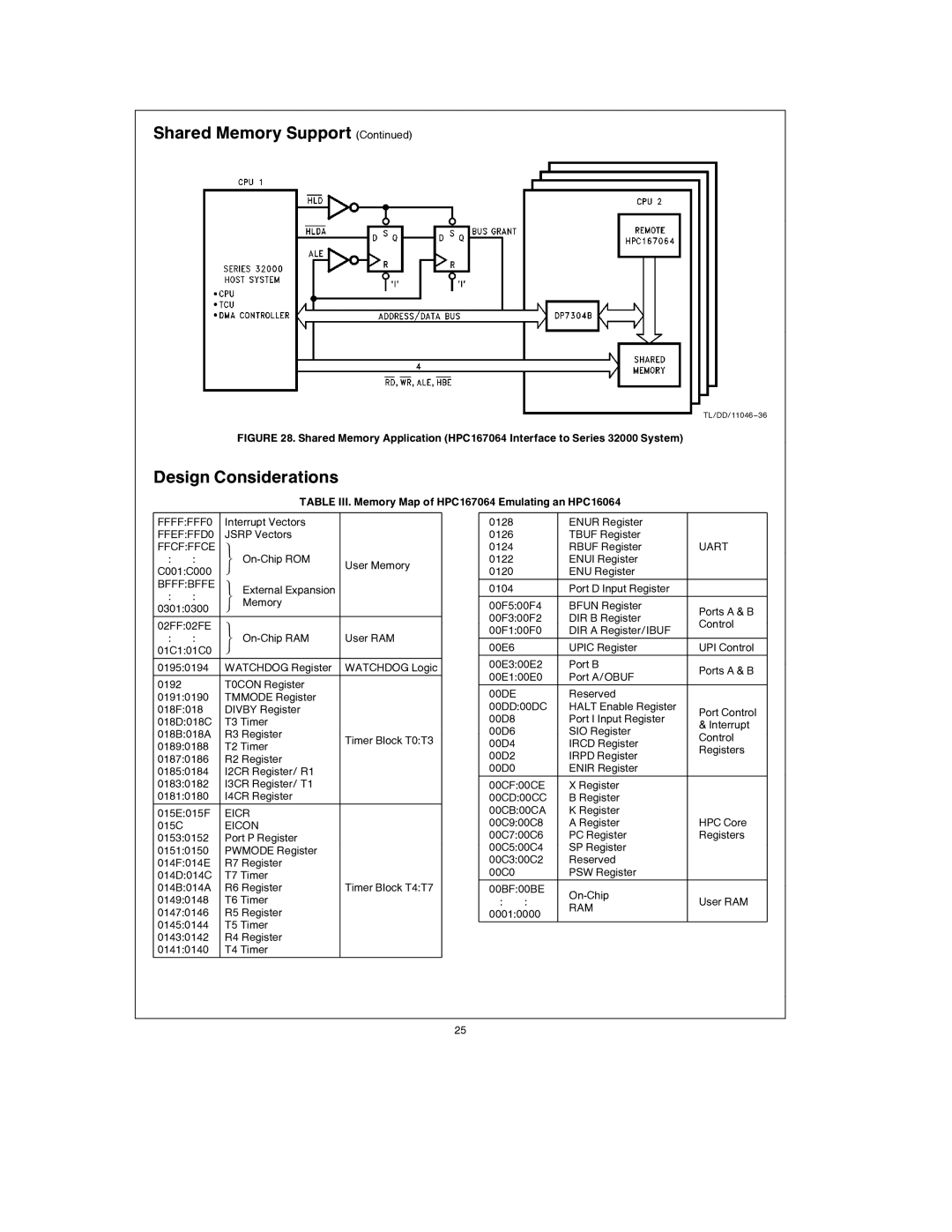

Shared Memory Support (Continued)

TL/DD/11046 – 36

FIGURE 28. Shared Memory Application (HPC167064 Interface to Series 32000 System)

Design Considerations

|

|

|

| TABLE III. Memory Map of HPC167064 Emulating an HPC16064 |

| |||||

|

|

|

|

|

|

|

| |||

FFFF:FFF0 | Interrupt Vectors |

|

| 0128 |

| ENUR Register |

| |||

FFEF:FFD0 | JSRP Vectors |

|

|

| 0126 |

| TBUF Register |

| ||

FFCF:FFCE |

|

|

|

|

| 0124 |

| RBUF Register | UART | |

: | : |

| User Memory |

| 0122 |

| ENUI Register |

| ||

C001:C000 |

|

|

|

| 0120 |

| ENU Register |

| ||

|

|

|

|

|

|

| ||||

BFFF:BFFE |

| External Expansion |

|

| 0104 |

| Port D Input Register |

| ||

: | : |

|

|

|

|

| ||||

| Memory |

|

|

| 00F5:00F4 | BFUN Register |

| |||

0301:0300 |

|

|

|

| Ports A & B | |||||

|

|

|

|

| ||||||

|

|

|

|

| 00F3:00F2 | DIR B Register | ||||

02FF:02FE | ( |

|

|

|

| Control | ||||

|

|

|

| 00F1:00F0 | DIR A Register/IBUF | |||||

: | : | User RAM |

|

| ||||||

| 00E6 |

| UPIC Register | UPI Control | ||||||

01C1:01C0 |

|

|

|

|

| |||||

|

|

|

|

|

|

| 00E3:00E2 | Port B |

| |

0195:0194 | WATCHDOG Register | WATCHDOG Logic |

| Ports A & B | ||||||

| 00E1:00E0 | Port A/OBUF | ||||||||

0192 |

| T0CON Register |

|

|

| |||||

|

|

| 00DE |

| Reserved |

| ||||

0191:0190 | TMMODE Register |

|

|

|

| |||||

|

| 00DD:00DC | HALT Enable Register |

| ||||||

018F:018 | DIVBY Register |

|

| Port Control | ||||||

|

| 00D8 |

| Port I Input Register | ||||||

018D:018C | T3 Timer |

|

|

|

| |||||

|

|

|

| & Interrupt | ||||||

|

|

| 00D6 |

| SIO Register | |||||

018B:018A | R3 Register |

|

|

|

| |||||

| Timer Block T0:T3 |

|

| Control | ||||||

|

| 00D4 |

| IRCD Register | ||||||

0189:0188 | T2 Timer |

|

|

| ||||||

|

|

| Registers | |||||||

|

|

|

| |||||||

|

|

| 00D2 |

| IRPD Register | |||||

0187:0186 | R2 Register |

|

|

|

| |||||

|

|

|

|

| ||||||

|

|

| 00D0 |

| ENIR Register |

| ||||

0185:0184 | I2CR Register/ R1 |

|

|

|

| |||||

0183:0182 | I3CR Register/ T1 |

|

| 00CF:00CE | X Register |

| ||||

0181:0180 | I4CR Register |

|

|

| 00CD:00CC | B Register |

| |||

015E:015F | EICR |

|

|

| 00CB:00CA | K Register |

| |||

|

|

| 00C9:00C8 | A Register | HPC Core | |||||

015C |

| EICON |

|

|

| |||||

|

|

|

| 00C7:00C6 | PC Register | Registers | ||||

0153:0152 | Port P Register |

|

|

| ||||||

|

|

| 00C5:00C4 | SP Register |

| |||||

0151:0150 | PWMODE Register |

|

|

| ||||||

|

| 00C3:00C2 | Reserved |

| ||||||

014F:014E | R7 Register |

|

|

|

| |||||

|

|

| 00C0 |

| PSW Register |

| ||||

014D:014C | T7 Timer |

|

|

|

|

| ||||

014B:014A | R6 Register |

| Timer Block T4:T7 |

| 00BF:00BE |

| ||||

0149:0148 | T6 Timer |

|

|

| : | : | User RAM | |||

|

|

| RAM | |||||||

0147:0146 | R5 Register |

|

|

| 0001:0000 |

| ||||

|

|

|

|

| ||||||

0145:0144 | T5 Timer |

|

|

|

|

|

|

| ||

0143:0142 | R4 Register |

|

|

|

|

|

|

| ||

0141:0140 | T4 Timer |

|

|

|

|

|

|

| ||

25