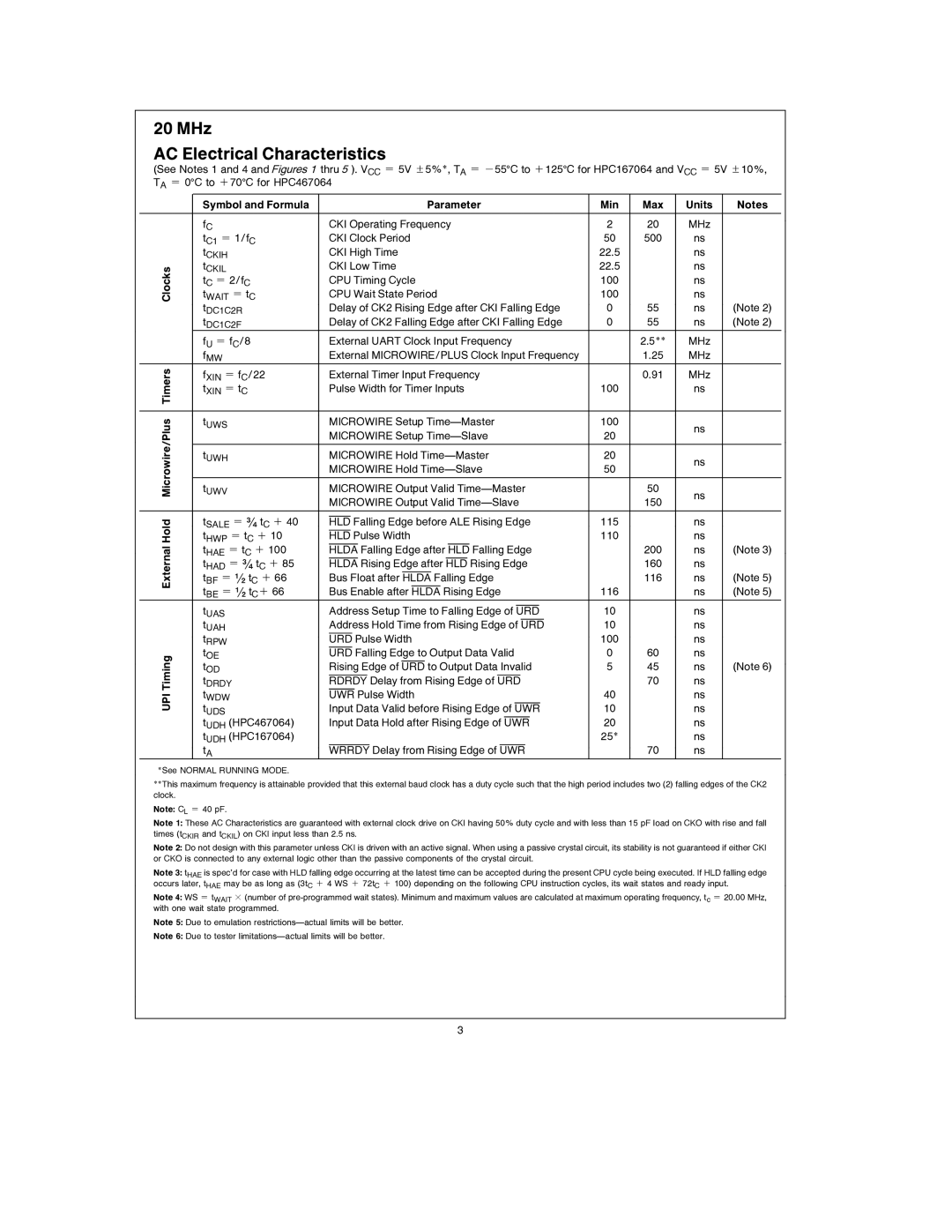

20 MHz

AC Electrical Characteristics

(See Notes 1 and 4 and Figures 1 thru 5 ). VCC e 5V g5%*, TA e b55§C to a125§C for HPC167064 and VCC e 5V g10%, TA e 0§C to a70§C for HPC467064

| Symbol and Formula |

|

|

|

|

|

|

|

|

| Parameter | Min | Max | Units | Notes | |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| fC |

| CKI Operating Frequency | 2 | 20 | MHz |

| |||||||||||||||||||

| tC1 e 1/fC |

| CKI Clock Period | 50 | 500 | ns |

| |||||||||||||||||||

| tCKIH |

| CKI High Time | 22.5 |

| ns |

| |||||||||||||||||||

Clocks | tCKIL |

| CKI Low Time | 22.5 |

| ns |

| |||||||||||||||||||

tWAIT e tC |

| CPU Wait State Period | 100 |

| ns |

| ||||||||||||||||||||

| tC e 2/fC |

| CPU Timing Cycle | 100 |

| ns |

| |||||||||||||||||||

| tDC1C2R |

| Delay of CK2 Rising Edge after CKI Falling Edge | 0 | 55 | ns | (Note 2) | |||||||||||||||||||

| tDC1C2F |

| Delay of CK2 Falling Edge after CKI Falling Edge | 0 | 55 | ns | (Note 2) | |||||||||||||||||||

| fU e fC/8 |

| External UART Clock Input Frequency |

| 2.5** | MHz |

| |||||||||||||||||||

| fMW |

| External MICROWIRE/PLUS Clock Input Frequency |

| 1.25 | MHz |

| |||||||||||||||||||

Timers | fXIN e fC/22 |

|

| External Timer Input Frequency |

| 0.91 | MHz |

| ||||||||||||||||||

|

|

|

| |||||||||||||||||||||||

| tXIN e tC |

| Pulse Width for Timer Inputs | 100 |

| ns |

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Microwire/Plus | tUWS |

| MICROWIRE Setup | 100 | 50 | ns |

| |||||||||||||||||||

tUWV |

| MICROWIRE Output Valid |

|

| ||||||||||||||||||||||

|

|

|

| MICROWIRE Setup | 20 |

|

|

| ||||||||||||||||||

| tUWH |

| MICROWIRE Hold | 20 |

| ns |

| |||||||||||||||||||

|

|

|

| MICROWIRE Hold | 50 |

|

| |||||||||||||||||||

|

|

|

|

|

|

| ||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MICROWIRE Output Valid |

| 150 | ns |

| ||||||||||||||||||

|

|

|

|

|

|

| ||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hold | tSALE e */4 tC a 40 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

HLD Falling Edge before ALE Rising Edge | 115 |

| ns |

| ||||||||||||||||||||||

tHWP e tC a 10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

HLD Pulse Width | 110 |

| ns |

| ||||||||||||||||||||||

External | tHAE e tC a 100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| HLDA Falling Edge after HLD Falling Edge |

| 200 | ns | (Note 3) | |||||||||||||||||||||

tHAD e */4 tC a 85 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| HLDA Rising Edge after HLD Rising Edge |

| 160 | ns |

| ||||||||||||||||||||

|

|

|

| |||||||||||||||||||||||

| tBF e (/2 tC a 66 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| Bus Float after HLDA Falling Edge |

| 116 | ns | (Note 5) | |||||||||||||||||||||

| tBE e (/2 tCa 66 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

| Bus Enable after HLDA Rising Edge | 116 |

| ns | (Note 5) | |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

| tUAS |

| Address Setup Time to Falling Edge of URD | 10 |

| ns |

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

| tUAH |

|

| Address Hold Time from Rising Edge of URD | 10 |

| ns |

| ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

| tRPW |

|

| URD Pulse Width | 100 |

| ns |

| ||||||||||||||||||

| tOE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

Timing |

|

| URD Falling Edge to Output Data Valid | 0 | 60 | ns |

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

tOD |

|

| Rising Edge of URD to Output Data Invalid | 5 | 45 | ns | (Note 6) | |||||||||||||||||||

|

|

| ||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

| tDRDY |

|

| RDRDY Delay from Rising Edge of URD |

| 70 | ns |

| ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

UPI | tWDW |

|

| UWR Pulse Width |

|

| 40 |

| ns |

| ||||||||||||||||

tUDS |

|

| Input Data Valid before Rising Edge of UWR | 10 |

| ns |

| |||||||||||||||||||

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

| tUDH (HPC467064) |

| Input Data Hold after Rising Edge of UWR | 20 |

| ns |

| |||||||||||||||||||

| tUDH (HPC167064) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 25* |

| ns |

|

| tA |

| WRRDY Delay from Rising Edge of UWR |

| 70 | ns |

| |||||||||||||||||||

*See NORMAL RUNNING MODE.

**This maximum frequency is attainable provided that this external baud clock has a duty cycle such that the high period includes two (2) falling edges of the CK2 clock.

Note: CL e 40 pF.

Note 1: These AC Characteristics are guaranteed with external clock drive on CKI having 50% duty cycle and with less than 15 pF load on CKO with rise and fall times (tCKIR and tCKIL) on CKI input less than 2.5 ns.

Note 2: Do not design with this parameter unless CKI is driven with an active signal. When using a passive crystal circuit, its stability is not guaranteed if either CKI or CKO is connected to any external logic other than the passive components of the crystal circuit.

Note 3: tHAE is spec’d for case with HLD falling edge occurring at the latest time can be accepted during the present CPU cycle being executed. If HLD falling edge occurs later, tHAE may be as long as (3tC a 4 WS a 72tC a 100) depending on the following CPU instruction cycles, its wait states and ready input.

Note 4: WS e tWAIT c (number of

Note 5: Due to emulation

Note 6: Due to tester

3