EN 90 |

| 9. |

| DVD963SA | Circuit Descriptions and List of Abbreviations |

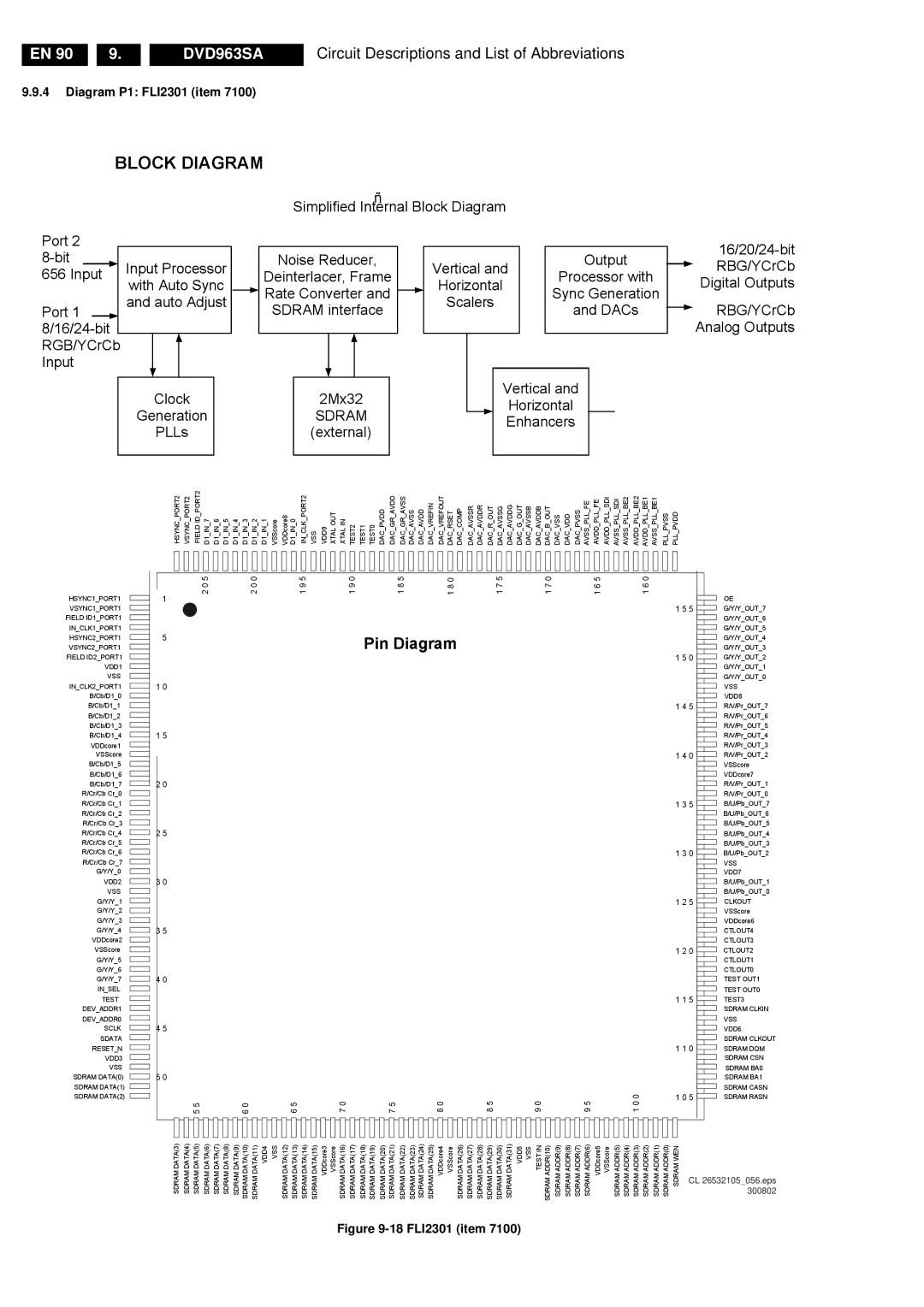

9.9.4Diagram P1: FLI2301 (item 7100)

BLOCK DIAGRAM

|

| ñ |

|

|

|

|

|

| |

|

| Simplified Internal Block Diagram |

|

|

|

| |||

Port 2 |

|

|

|

|

|

|

| ||

| Noise Reducer, |

|

| Output | |||||

Input Processor | Vertical and | RBG/YCrCb | |||||||

656 Input | Deinterlacer, Frame | Processor with | |||||||

with Auto Sync | Horizontal | Digital Outputs | |||||||

| Rate Converter and | Sync Generation | |||||||

| and auto Adjust | Scalers |

| ||||||

Port 1 | SDRAM interface | and DACs | RBG/YCrCb | ||||||

|

|

| |||||||

|

|

|

|

|

|

| Analog Outputs | ||

RGB/YCrCb |

|

|

|

|

|

|

|

| |

Input |

|

|

|

|

|

|

|

| |

| Clock | 2Mx32 |

| Vertical and |

| ||||

|

|

| Horizontal |

|

|

| |||

| Generation | SDRAM |

|

|

| ||||

|

| Enhancers |

| ||||||

| PLLs | (external) |

|

| |||||

|

|

|

|

|

|

| |||

PLL_PVDD

PLL_PVSS

AVSS_PLL_BE1

AVDD_PLL_BE1

AVDD_PLL_BE2

AVSS_PLL_BE2

AVSS_PLL_SDI

AVDD_PLL_SDI

AVDD_PLL_FE

AVSS_PLL_FE

DAC_PVSS

DAC_VDD

DAC_VSS

DAC_B_OUT

DAC_AVDDB

DAC_AVSSB

DAC_G_OUT

DAC_AVDDG

DAC_AVSSG

DAC_R_OUT

DAC_AVDDR

DAC_AVSSR

DAC_COMP

DAC_RSET

DAC_VREFOUT

DAC_VREFIN

DAC_AVDD

DAC_AVSS

DAC_GR_AVSS

DAC_GR_AVDD

DAC_PVDD

TEST0

TEST1

TEST2

XTAL IN

XTAL OUT

VDD9

VSS

IN_CLK_PORT2

D1_IN_0

VDDcore8

VSScore

D1_IN_1

D1_IN_2

D1_IN_3

D1_IN_4

D1_IN_5

D1_IN_6

D1_IN_7

FIELD ID_PORT2

VSYNC_PORT2

HSYNC_PORT2

HSYNC1_PORT1 VSYNC1_PORT1 FIELD ID1_PORT1 IN_CLK1_PORT1 HSYNC2_PORT1 VSYNC2_PORT1 FIELD ID2_PORT1 VDD1

VSS IN_CLK2_PORT1 B/Cb/D1_0 B/Cb/D1_1 B/Cb/D1_2 B/Cb/D1_3 B/Cb/D1_4

VDDcore1

VSScore B/Cb/D1_5 B/Cb/D1_6 B/Cb/D1_7 R/Cr/Cb Cr_0 R/Cr/Cb Cr_1 R/Cr/Cb Cr_2 R/Cr/Cb Cr_3 R/Cr/Cb Cr_4 R/Cr/Cb Cr_5 R/Cr/Cb Cr_6 R/Cr/Cb Cr_7 G/Y/Y_0 VDD2

VSS G/Y/Y_1 G/Y/Y_2 G/Y/Y_3 G/Y/Y_4

VDDcore2

VSScore

G/Y/Y_5

G/Y/Y_6

G/Y/Y_7

IN_SEL

TEST DEV_ADDR1 DEV_ADDR0

SCLK

SDATA RESET_N VDD3

VSS SDRAM DATA(0) SDRAM DATA(1) SDRAM DATA(2)

2 0 5 | 2 0 0 | 1 9 5 | 1 9 0 | 1 8 5 | 1 8 0 | 1 7 5 | 1 7 0 | 1 6 5 | 1 6 0 |

1 |

|

|

|

|

|

|

|

|

|

5 |

|

|

| Pin Diagram |

|

|

|

| |

|

|

|

|

|

|

|

| ||

10

15

20

25

30

35

40

45

50

|

|

|

| 5 5 |

|

|

|

|

|

| 6 0 |

|

|

|

|

|

|

| 6 5 |

|

|

|

| 7 0 |

|

|

|

|

| 7 5 |

|

|

|

|

|

|

| 8 0 |

|

|

|

|

|

|

| 8 5 |

|

|

|

|

|

|

| 9 0 |

|

|

|

|

|

|

| 9 5 |

|

|

|

|

|

|

| 1 0 0 |

|

|

|

|

| ||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDRAM DATA(3) | SDRAM DATA(4) | SDRAM DATA(5) | SDRAM DATA(6) | SDRAM DATA(7) | SDRAM DATA(8) | SDRAM DATA(9) SDRAM DATA(10) | SDRAM DATA(11) | VDD4 | VSS | SDRAM DATA(12) | SDRAM DATA(13) | SDRAM DATA(14) | SDRAM DATA(15) | VDDcore3 VSScore SDRAM DATA(16) | SDRAM DATA(17) | SDRAM DATA(18) SDRAM DATA(19) | SDRAM DATA(20) SDRAM DATA(21) | SDRAM DATA(22) | SDRAM DATA(23) SDRAM DATA(24) | SDRAM DATA(25) | VDDcore4 | VSScore | SDRAM DATA(26) | SDRAM DATA(27) | SDRAM DATA(28) | SDRAM DATA(29) | SDRAM DATA(30) | SDRAM DATA(31) | VDD5 VSS | TEST IN SDRAM ADDR(10) | SDRAM ADDR(9) | SDRAM ADDR(8) | SDRAM ADDR(7) | SDRAM ADDR(6) | VDDcore5 VSScore | SDRAM ADDR(5) SDRAM ADDR(4) | SDRAM ADDR(3) | SDRAM ADDR(2) | SDRAM ADDR(1) | SDRAM ADDR(0) | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

| OE |

1 5 5 |

|

| ||

|

| |||

|

| G/Y/Y_OUT_7 | ||

|

| |||

|

|

|

| G/Y/Y_OUT_6 |

|

|

|

| |

|

|

|

| G/Y/Y_OUT_5 |

|

|

|

| |

|

|

|

| G/Y/Y_OUT_4 |

1 5 0 |

|

| G/Y/Y_OUT_3 | |

|

| G/Y/Y_OUT_2 | ||

|

|

|

| G/Y/Y_OUT_1 |

|

|

|

| G/Y/Y_OUT_0 |

|

|

|

| VSS |

1 4 5 |

|

| VDD8 | |

|

| R/V/Pr_OUT_7 | ||

|

|

|

| R/V/Pr_OUT_6 |

|

|

|

| R/V/Pr_OUT_5 |

|

|

|

| R/V/Pr_OUT_4 |

1 4 0 |

|

| R/V/Pr_OUT_3 | |

|

| R/V/Pr_OUT_2 | ||

|

|

|

| VSScore |

|

|

|

| VDDcore7 |

|

|

|

| R/V/Pr_OUT_1 |

1 3 5 |

|

| R/V/Pr_OUT_0 | |

|

| B/U/Pb_OUT_7 | ||

|

|

|

| B/U/Pb_OUT_6 |

|

|

|

| B/U/Pb_OUT_5 |

|

|

|

| B/U/Pb_OUT_4 |

1 3 0 |

|

| B/U/Pb_OUT_3 | |

|

| B/U/Pb_OUT_2 | ||

|

|

|

| VSS |

|

|

|

| VDD7 |

|

|

|

| B/U/Pb_OUT_1 |

1 2 5 |

|

| B/U/Pb_OUT_0 | |

|

| CLKOUT | ||

|

|

|

| VSScore |

|

|

|

| VDDcore6 |

|

|

|

| CTLOUT4 |

1 2 0 |

|

| CTLOUT3 | |

|

| CTLOUT2 | ||

|

|

|

| CTLOUT1 |

|

|

|

| CTLOUT0 |

|

|

|

| TEST OUT1 |

1 1 5 |

|

| TEST OUT0 | |

|

| TEST3 | ||

|

|

|

| SDRAM CLKIN |

|

|

|

| VSS |

|

|

|

| VDD6 |

1 1 0 |

|

| SDRAM CLKOUT | |

|

| SDRAM DQM | ||

|

|

|

| SDRAM CSN |

|

|

|

| SDRAM BA0 |

|

|

|

| SDRAM BA1 |

1 0 5 |

|

| SDRAM CASN | |

|

| SDRAM RASN | ||

|

|

|

|

|

|

|

|

|

|

SDRAM WEN | CL 26532105_056.eps |

| 300802 |