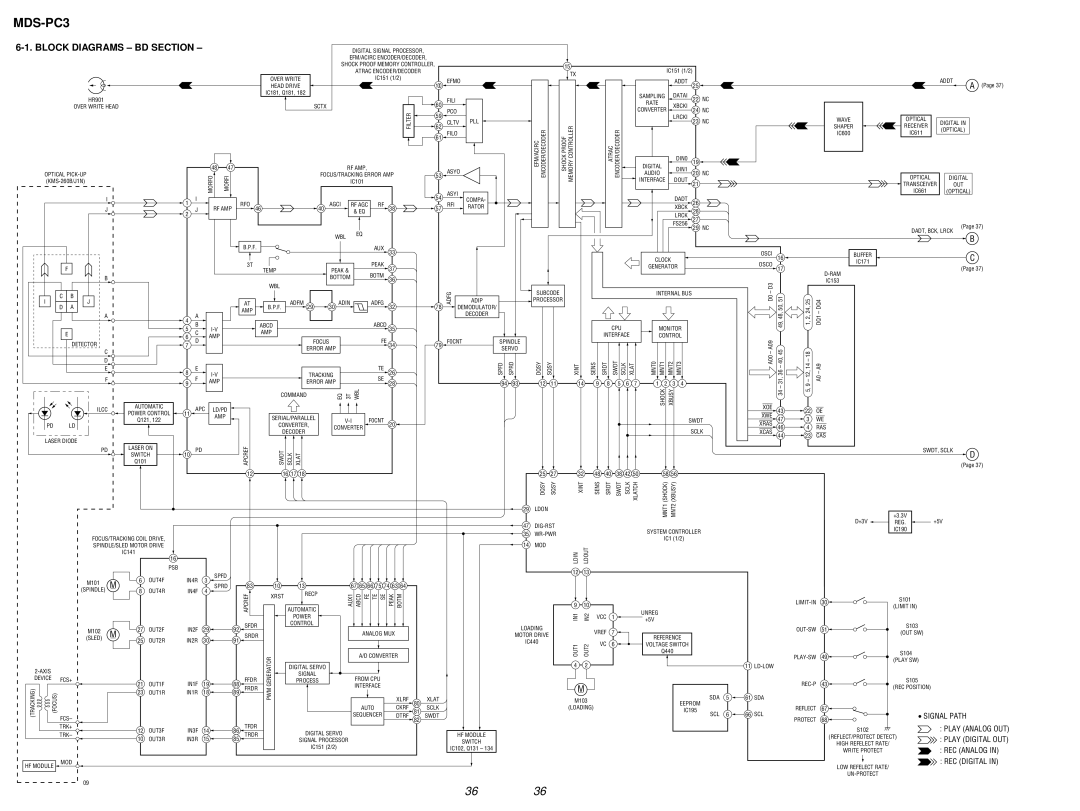

MDS-PC3

|

|

|

|

| DIGITAL SIGNAL PROCESSOR, |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

| EFM/ACIRC ENCODER/DECODER, |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| SHOCK PROOF MEMORY CONTROLLER, |

|

|

| 15 |

| IC151 (1/2) |

| |||

|

|

|

|

|

| ATRAC ENCODER/DECODER |

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| TX |

|

| ||||

|

|

|

| OVER WRITE |

|

| IC151 (1/2) |

|

|

|

|

|

|

|

| |

|

|

|

|

|

| EFMO |

|

|

|

|

|

| ADDT |

| ||

|

|

|

| HEAD DRIVE |

|

|

| 100 |

|

|

|

|

|

| 25 |

|

|

|

|

| IC181, Q181, 182 |

|

|

|

|

|

|

|

|

| SAMPLING | DATAI | NC |

HR901 |

|

|

|

|

|

|

| FILI |

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| RATE | 22 | |||

OVER WRITE HEAD |

|

|

|

| SCTX |

|

| 60 |

|

|

|

|

| XBCKI |

| |

|

|

|

|

|

|

|

|

|

|

| CONVERTER |

| ||||

|

|

|

|

|

|

|

| PCO |

|

|

|

|

| 24 NC | ||

|

|

|

|

|

|

|

| 59 | PLL |

|

|

|

|

| LRCKI | NC |

|

|

|

|

|

|

|

| CLTV |

|

|

|

|

| 23 | ||

|

|

|

|

|

|

|

| 62 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| FILO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 61 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DIN0 |

|

|

| 48 | 47 |

|

| RF AMP, |

|

|

|

|

|

|

| DIGITAL | 19 |

|

|

|

|

|

| ASYO |

|

|

|

|

| DIN1 |

| ||||

OPTICAL |

|

|

|

| FOCUS/TRACKING ERROR AMP |

|

|

|

|

| AUDIO | 20 | NC | |||

|

|

|

| 53 |

|

|

|

|

| |||||||

|

| MORFO | MORFI |

|

| IC101 | FILTER |

|

| EFM/ACIRC ENCODER/DECODER | SHOCKPROOF | CONTROLLERMEMORY | ATRAC ENCODER/DECODER | INTERFACE | DOUT |

|

|

|

|

|

|

|

|

| 21 |

| |||||||

|

|

|

|

| ASYI |

|

|

|

| |||||||

I | I |

|

| RFO | AGCI | RF AGC | RF | 54 | COMPA- |

|

|

|

|

| DADT |

|

1 |

|

|

| RFI | RATOR |

|

|

|

|

| 26 |

| ||||

J | J | RF AMP | 46 | 40 | & EQ | 38 | 57 |

|

|

|

|

| XBCK |

| ||

|

|

|

|

|

| 28 |

| |||||||||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| LRCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| FS256 |

|

ADDT | A (Page 37) |

|

|

|

|

|

|

|

| WAVE |

| OPTICAL |

| DIGITAL IN |

| SHAPER |

| RECEIVER |

| |

| IC600 |

| IC611 |

| (OPTICAL) |

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

OPTICAL | DIGITAL |

TRANSCEIVER | OUT |

IC661 | (OPTICAL) |

29 NC |

EQ |

DADT, BCK, LRCK

(Page 37)

WBL |

| B.P.F. |

| AUX | 33 |

|

|

|

|

|

| |

| 3T |

| PEAK |

| CLOCK |

F | PEAK & | 37 | GENERATOR | ||

TEMP | BOTM |

| |||

| B | BOTTOM | 36 |

| |

|

|

|

|

|

|

|

|

|

| WBL |

|

|

|

|

|

|

|

|

|

| SUBCODE |

|

|

|

|

|

|

|

|

|

| |

C | B |

|

|

|

|

|

|

|

|

|

|

|

|

| ADFG |

|

|

|

|

|

|

|

| INTERNAL BUS | |||||

|

|

|

|

|

|

|

|

|

|

|

|

| ADIP |

| PROCESSOR |

|

|

|

|

|

|

|

|

|

| ||||

I | J |

|

|

|

| AT |

| ADFM |

|

| ADIN | ADFG |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

D | A |

|

|

|

| B.P.F. | 29 | 30 | 32 | 78 | DEMODULATOR/ |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

| A |

|

| A |

| AMP |

|

|

|

|

|

|

|

|

| DECODER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

| B |

|

| ABCD |

|

|

|

| ABCD 35 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

| 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| CPU |

|

| MONITOR | ||||||||

|

|

| C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

| E |

| 6 | AMP |

| AMP |

|

|

|

|

|

|

|

|

|

|

|

|

|

| INTERFACE |

| CONTROL | ||||||

|

| D |

|

|

|

| FOCUS |

| FE |

|

| F0CNT | SPINDLE |

|

|

|

|

| |||||||||||

| DETECTOR |

| 7 |

|

|

|

|

|

| 34 | 79 |

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

| ERROR AMP |

|

|

| SERVO |

|

|

|

|

|

|

|

|

|

|

|

| ||||||

| C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| D |

|

|

|

|

|

|

|

|

|

|

|

|

|

| SPFD | SPRD | DQSY | SQSY | XINT | SENS | SRDT | SWDT SCLK | XLAT |

| MNT0 | MNT1 | MNT2 | MNT3 |

| E |

| 8 | E |

|

|

| TRACKING |

| TE | 26 |

|

|

| |||||||||||||||

| F |

| F |

|

|

|

| SE |

|

|

| ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

| 9 | AMP |

|

|

| ERROR AMP |

| 28 |

|

| 94 | 93 | 12 | 11 | 14 | 9 | 8 | 5 | 6 | 7 | 1 | 2 | 3 | 4 | ||||

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

| COMMAND |

| EQ 3T | WBL |

|

|

|

|

|

|

|

|

|

|

|

|

|

| SHOCK | XBUSY |

| ||

| ILCC | AUTOMATIC |

| APC | LD/PD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| POWER CONTROL | 11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

| AMP |

| SERIAL/PARALLEL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

| Q121, 122 |

|

|

| F0CNT | 20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SWDT | ||||||

PD | LD |

|

|

|

| CONVERTER, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

| CONVERTER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SCLK | ||||||||

|

|

|

|

|

|

| DECODER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

LASER DIODE | LASER ON |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| PD | 10 | PD |

| APCREF | SWDT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| SWITCH |

| SCLK XLAT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

| Q101 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

OSCI | 16 |

|

| |

OSCO |

|

| ||

17 |

|

| ||

|

| |||

|

|

| ||

D0 – D3 |

|

| IC153 | |

49, 48, 50, 51 | 1, 2, 24, 25 | DQ1 – DQ4 | ||

A00 – A09 | – 40, 45 | 14 – 18 | A9 | |

| 34 – 31, 36 | 5, 9 – 12, | A0 – | |

XOE | 43 | 22 | OE | |

XWE | ||||

47 | 3 | WE | ||

XRAS | ||||

46 | 4 | RAS | ||

XCAS | ||||

44 | 23 | CAS | ||

|

BUFFER

IC171

![]() B

B

C

(Page 37)

SWDT, SCLK

![]() D

D

|

|

|

|

|

| 12 |

| 16 17 18 |

|

| 25 | 27 | 32 | 48 | 40 | 38 42 50 | 58 56 | |||

|

|

|

|

|

|

|

|

|

|

|

| DQSY | SQSY | XINT | SENS | SRDT | SWDT | SCLK XLATCH | (SHOCK) | (XBUSY) |

|

|

|

|

|

|

|

|

|

|

| 29 | LDON |

|

|

|

|

|

| MNT1 | MNT2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| 47 |

|

|

|

|

| SYSTEM CONTROLLER | |||

|

|

|

|

|

|

|

|

|

|

| 35 |

|

|

|

|

| ||||

FOCUS/TRACKING COIL DRIVE, |

|

|

|

|

|

|

|

|

|

|

|

| IC1 (1/2) | |||||||

|

|

|

|

|

|

| 14 | MOD |

|

|

|

|

|

| ||||||

SPINDLE/SLED MOTOR DRIVE |

|

|

|

|

|

|

|

| LDOUT |

|

|

|

|

|

| |||||

|

| IC141 |

| 16 |

|

|

|

|

|

|

|

| LDIN |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

| PSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| 12 | 13 |

|

|

|

|

|

| |

|

|

|

|

| SPFD |

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| 6 | OUT4F | IN4R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

M101 | M | 3 | 83 | 10 |

| 13 | 67 65 66 75 74 63 64 |

|

|

|

|

|

|

|

|

| ||||

|

|

| 4 SPRD |

|

|

|

|

|

|

|

|

|

| |||||||

(SPINDLE) | 8 | OUT4R | IN4F |

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

| APCREF | XRST | RECP | AUX1 ABCD FE TE SE PEAK | BOTM |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

| AUTOMATIC |

| 9 | 10 |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

| IN1 | IN2 |

|

|

|

| UNREG |

| ||||

|

|

|

|

|

|

|

|

| POWER |

|

|

| VCC | 1 |

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

| +5V |

| ||||||

|

| 27 | OUT2F | IN2F | 29 | SFDR |

|

| CONTROL |

| LOADING |

|

|

|

|

|

|

|

| |

M102 | M | 92 |

|

|

| ANALOG MUX |

|

| VREF | 7 |

|

|

| |||||||

(SLED) |

| OUT2R | IN2R |

| SRDR |

|

|

| MOTOR DRIVE |

|

|

| REFERENCE | |||||||

| 25 | 30 | 91 |

|

|

|

| IC440 |

|

| VC | 6 |

| |||||||

|

|

|

|

|

| OUT1 | OUT2 |

| VOLTAGE SWITCH | |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

D+3V ![]()

![]()

![]()

(Page 37)

+3.3V

REG. ![]() +5V IC190

+5V IC190

S101

(LIMIT IN)

S103

(OUT SW)

|

|

|

|

|

|

|

|

|

| A/D CONVERTER |

|

|

| Q440 |

| |

|

|

|

|

|

|

|

| GENERATOR |

|

|

|

|

|

| ||

|

|

|

|

|

|

| DIGITAL SERVO |

|

|

| 4 | 2 |

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| SIGNAL |

|

|

|

|

|

|

| ||

DEVICE |

| FCS+ |

|

|

|

| FFDR | FROM CPU |

|

|

|

|

|

| ||

| OUT1F | IN1F | 19 | 88 | PROCESS |

|

|

|

|

|

| |||||

|

| 21 | FRDR |

| INTERFACE |

|

|

| M |

|

| |||||

(TRACKING) | (FOCUS) | 23 | OUT1R | IN1R | 18 | 89 | PWM |

|

|

|

|

| SDA | 5 | ||

|

|

| XLRF | XLAT |

|

| ||||||||||

|

|

|

|

|

|

|

| M103 | ||||||||

|

|

|

|

|

|

|

| EEPROM |

| |||||||

|

|

|

|

|

|

| AUTO | CKRF | 80 | (LOADING) |

| |||||

|

|

|

|

|

|

| SCLK | IC195 |

| |||||||

|

|

|

|

|

|

| SEQUENCER | DTRF | 81 |

|

| 6 | ||||

FCS– |

|

|

|

|

|

| SWDT |

|

| SCL | ||||||

|

|

|

|

|

| TFDR |

|

|

|

| 82 |

|

|

|

| |

|

| TRK+ | OUT3F | IN3F | 14 | 86 |

|

|

|

|

|

|

|

|

| |

|

| 12 | TRDR |

| DIGITAL SERVO |

|

|

| HF MODULE |

|

|

| ||||

|

| TRK– |

|

|

|

|

|

|

|

|

|

|

| |||

|

| 10 | OUT3R | IN3R | 15 | 85 |

|

| SIGNAL PROCESSOR |

|

|

| SWITCH |

|

|

|

|

|

|

|

|

|

|

|

| IC151 (2/2) |

|

|

| IC102, Q131 – 134 |

|

|

|

HF MODULE | MOD |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| 09 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

49 | S104 |

| |

(PLAY SW) |

| ||

11 |

|

| |

|

|

| |

43 | S105 |

| |

(REC POSITION) |

| ||

|

|

| |

61 SDA |

|

|

|

REFLECT | 67 |

|

|

66 SCL | 68 | • SIGNAL PATH | |

PROTECT |

|

| |

| S102 |

| : PLAY (ANALOG OUT) |

| (REFLECT/PROTECT DETECT) | : PLAY (DIGITAL OUT) | |

| HIGH REFELECT RATE/ |

| |

|

| : REC (ANALOG IN) | |

| WRITE PROTECT |

| |

: REC (DIGITAL IN)

LOW REFELECT RATE/

36 36