Appendix B: BIOS POST Codes

Appendix B

BIOS POST Codes

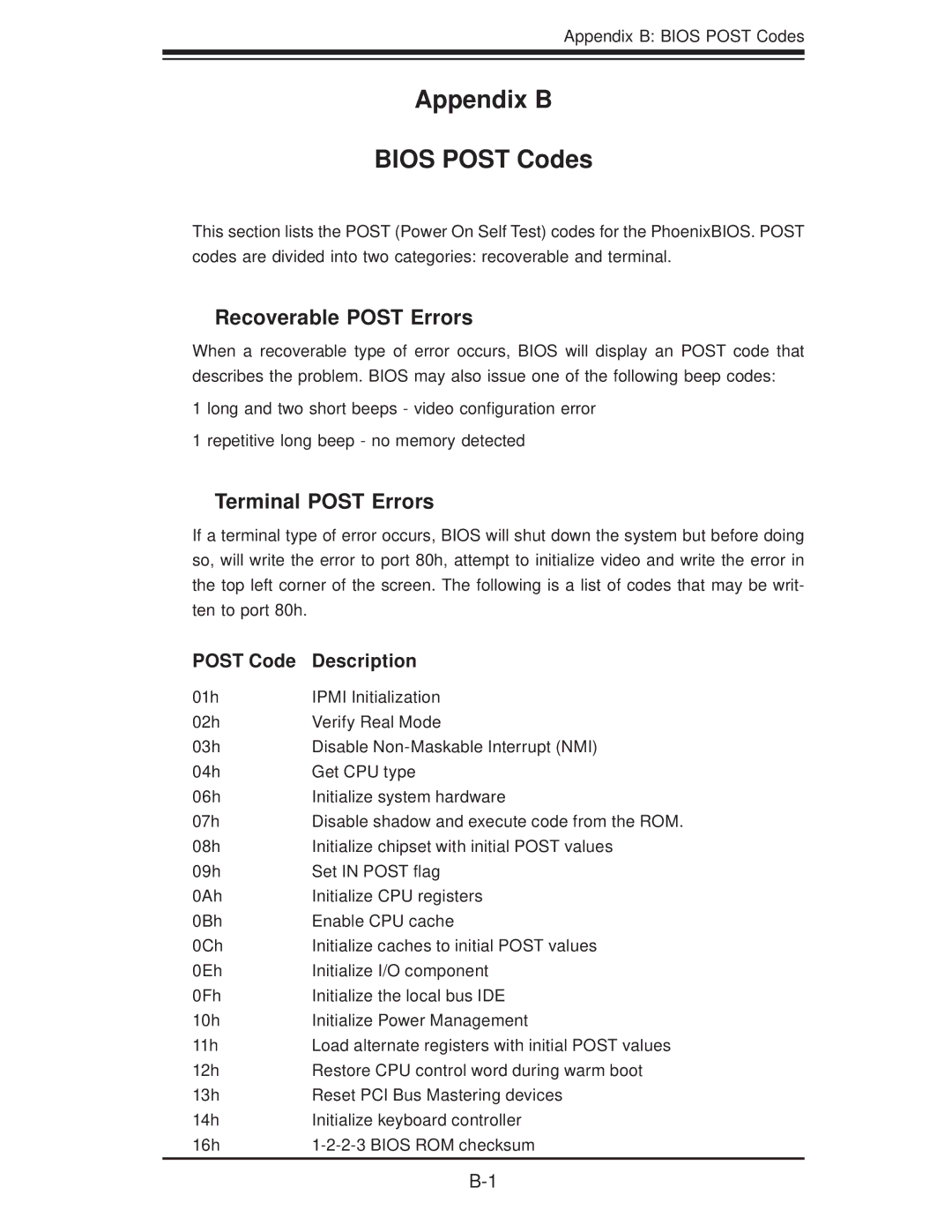

This section lists the POST (Power On Self Test) codes for the PhoenixBIOS. POST codes are divided into two categories: recoverable and terminal.

Recoverable POST Errors

When a recoverable type of error occurs, BIOS will display an POST code that describes the problem. BIOS may also issue one of the following beep codes:

1 long and two short beeps - video configuration error

1 repetitive long beep - no memory detected

Terminal POST Errors

If a terminal type of error occurs, BIOS will shut down the system but before doing so, will write the error to port 80h, attempt to initialize video and write the error in the top left corner of the screen. The following is a list of codes that may be writ- ten to port 80h.

POST Code | Description |

01h | IPMI Initialization |

02h | Verify Real Mode |

03h | Disable |

04h | Get CPU type |

06h | Initialize system hardware |

07h | Disable shadow and execute code from the ROM. |

08h | Initialize chipset with initial POST values |

09h | Set IN POST flag |

0Ah | Initialize CPU registers |

0Bh | Enable CPU cache |

0Ch | Initialize caches to initial POST values |

0Eh | Initialize I/O component |

0Fh | Initialize the local bus IDE |

10h | Initialize Power Management |

11h | Load alternate registers with initial POST values |

12h | Restore CPU control word during warm boot |

13h | Reset PCI Bus Mastering devices |

14h | Initialize keyboard controller |

16h |