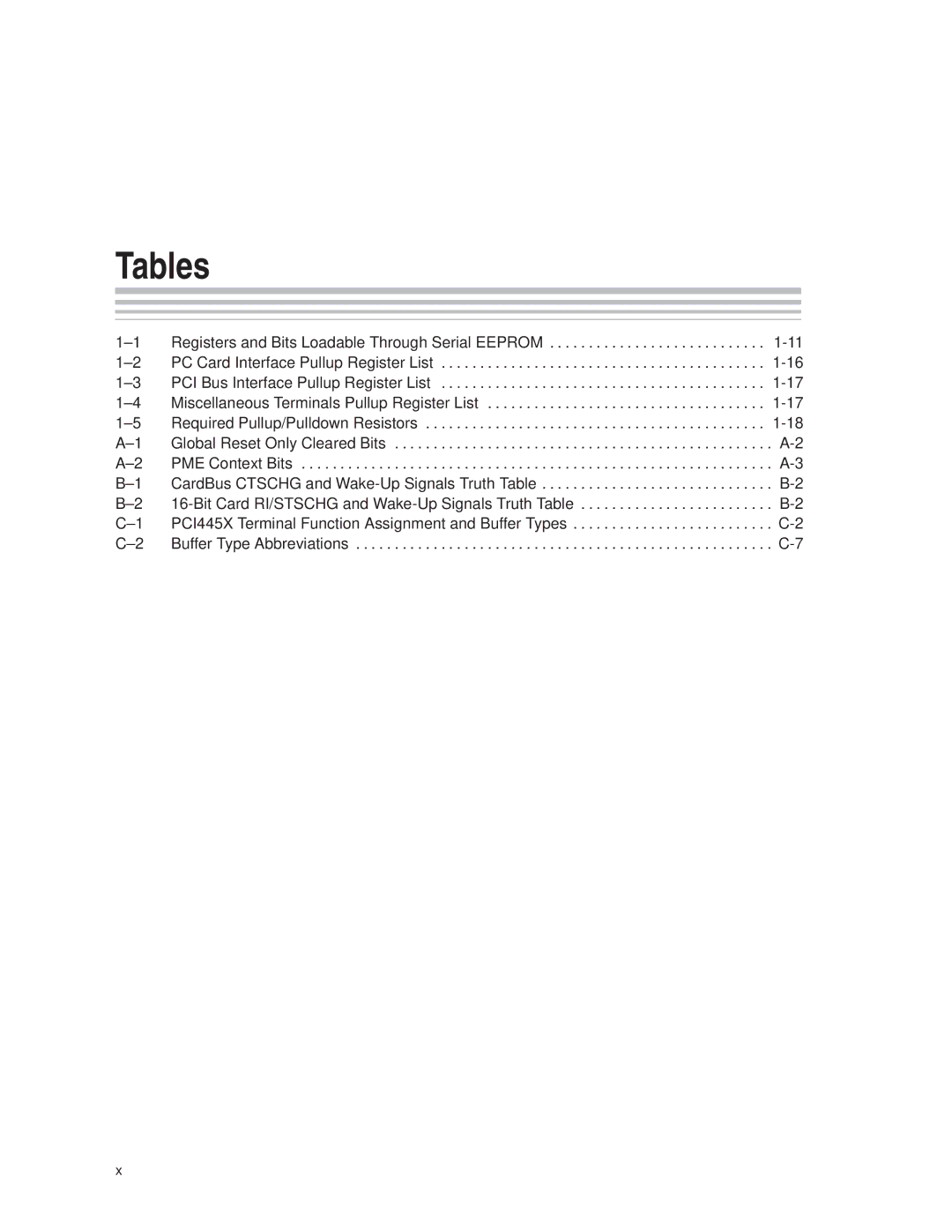

Tables

1±1 | Registers and Bits Loadable Through Serial EEPROM | |

1±2 | PC Card Interface Pullup Register List | |

1±3 | PCI Bus Interface Pullup Register List | |

1±4 | Miscellaneous Terminals Pullup Register List | |

1±5 | Required Pullup/Pulldown Resistors | |

A±1 | Global Reset Only Cleared Bits | |

A±2 | PME Context Bits | |

B±1 | CardBus CTSCHG and | |

B±2 | ||

C±1 | PCI445X Terminal Function Assignment and Buffer Types | |

C±2 | Buffer Type Abbreviations |

x