System Implementation

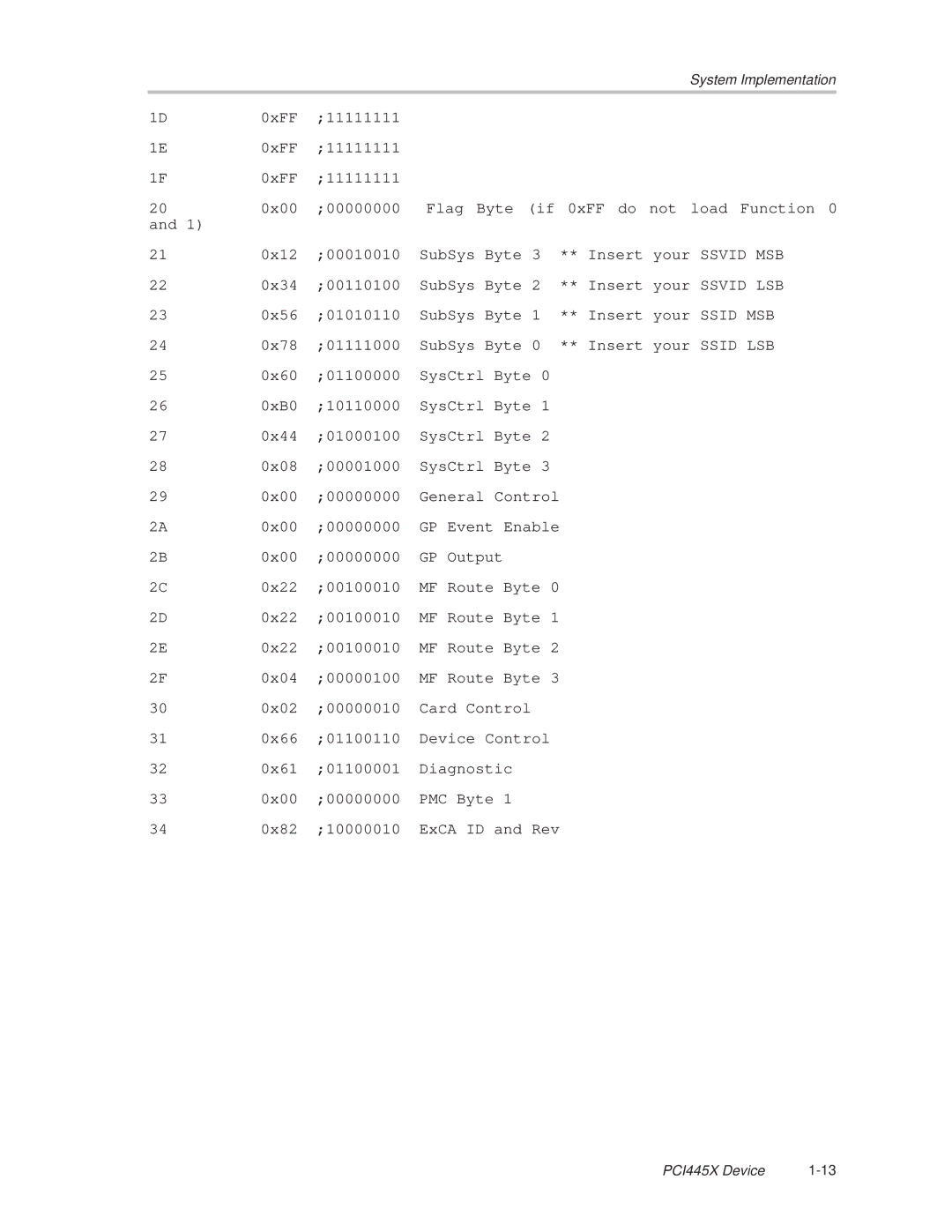

1D 0xFF ;11111111

1E 0xFF ;11111111

1F 0xFF ;11111111

200x00 ;00000000 Flag Byte (if 0xFF do not load Function 0

and 1)

210x12 ;00010010 SubSys Byte 3 ** Insert your SSVID MSB

220x34 ;00110100 SubSys Byte 2 ** Insert your SSVID LSB

230x56 ;01010110 SubSys Byte 1 ** Insert your SSID MSB

240x78 ;01111000 SubSys Byte 0 ** Insert your SSID LSB

250x60 ;01100000 SysCtrl Byte 0

260xB0 ;10110000 SysCtrl Byte 1

270x44 ;01000100 SysCtrl Byte 2

280x08 ;00001000 SysCtrl Byte 3

290x00 ;00000000 General Control

2A | 0x00 | ;00000000 | GP Event Enable |

2B | 0x00 | ;00000000 | GP Output |

2C | 0x22 | ;00100010 | MF Route Byte 0 |

2D | 0x22 | ;00100010 | MF Route Byte 1 |

2E | 0x22 | ;00100010 | MF Route Byte 2 |

2F | 0x04 | ;00000100 | MF Route Byte 3 |

300x02 ;00000010 Card Control

310x66 ;01100110 Device Control

320x61 ;01100001 Diagnostic

330x00 ;00000000 PMC Byte 1

340x82 ;10000010 ExCA ID and Rev

PCI445X Device |