TS32M~1GCF80 |

|

|

|

|

| 80X CompactFlash Card | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

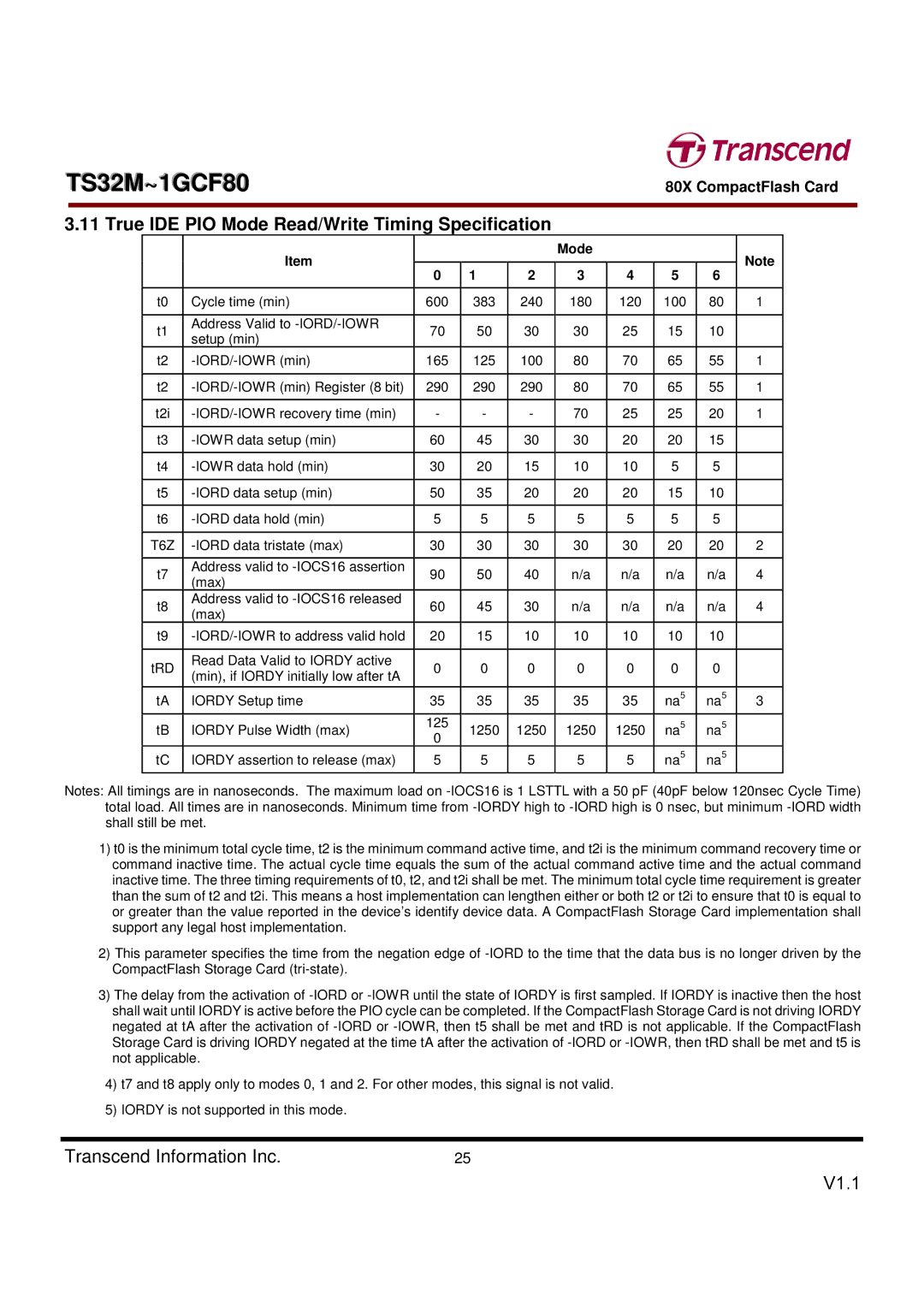

3.11 True IDE PIO Mode Read/Write Timing Specification |

|

|

|

|

|

|

| ||||||

|

|

| Item |

|

|

| Mode |

|

|

| Note |

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | ||||

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| t0 | Cycle time (min) | 600 | 383 | 240 | 180 | 120 | 100 | 80 | 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| t1 | Address Valid to | 70 | 50 | 30 | 30 | 25 | 15 | 10 |

|

|

|

|

| setup (min) |

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| t2 | 165 | 125 | 100 | 80 | 70 | 65 | 55 | 1 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| t2 | 290 | 290 | 290 | 80 | 70 | 65 | 55 | 1 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| t2i | - | - | - | 70 | 25 | 25 | 20 | 1 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| t3 | 60 | 45 | 30 | 30 | 20 | 20 | 15 |

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| t4 | 30 | 20 | 15 | 10 | 10 | 5 | 5 |

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| t5 | 50 | 35 | 20 | 20 | 20 | 15 | 10 |

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| t6 | 5 | 5 | 5 | 5 | 5 | 5 | 5 |

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| T6Z | 30 | 30 | 30 | 30 | 30 | 20 | 20 | 2 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| t7 | Address valid to | 90 | 50 | 40 | n/a | n/a | n/a | n/a | 4 |

|

|

|

| (max) |

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| t8 | Address valid to | 60 | 45 | 30 | n/a | n/a | n/a | n/a | 4 |

|

|

|

| (max) |

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| t9 | 20 | 15 | 10 | 10 | 10 | 10 | 10 |

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tRD | Read Data Valid to IORDY active | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

|

|

|

| (min), if IORDY initially low after tA |

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tA | IORDY Setup time | 35 | 35 | 35 | 35 | 35 | na5 | na5 | 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| tB | IORDY Pulse Width (max) | 125 | 1250 | 1250 | 1250 | 1250 | na5 | na5 |

|

|

|

|

|

|

| 0 |

|

|

|

|

|

|

|

|

|

|

| tC | IORDY assertion to release (max) | 5 | 5 | 5 | 5 | 5 | na5 | na5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Notes: All timings are in nanoseconds. The maximum load on

1)t0 is the minimum total cycle time, t2 is the minimum command active time, and t2i is the minimum command recovery time or command inactive time. The actual cycle time equals the sum of the actual command active time and the actual command inactive time. The three timing requirements of t0, t2, and t2i shall be met. The minimum total cycle time requirement is greater than the sum of t2 and t2i. This means a host implementation can lengthen either or both t2 or t2i to ensure that t0 is equal to or greater than the value reported in the device’s identify device data. A CompactFlash Storage Card implementation shall support any legal host implementation.

2)This parameter specifies the time from the negation edge of

3)The delay from the activation of

4)t7 and t8 apply only to modes 0, 1 and 2. For other modes, this signal is not valid.

5)IORDY is not supported in this mode.

Transcend Information Inc. | 25 |