TS32M~1GCF80 |

|

|

|

|

|

| 80X CompactFlash Card | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

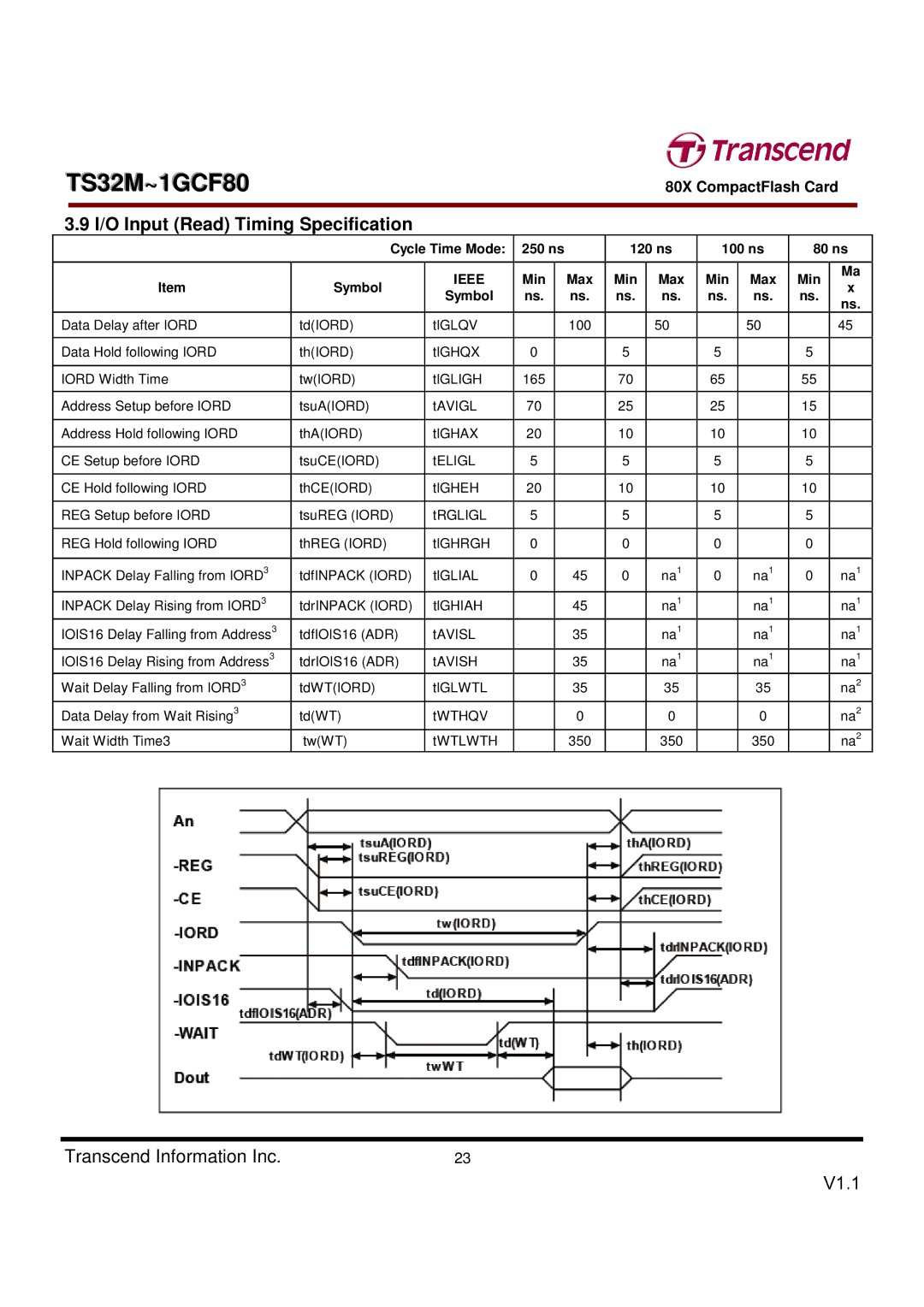

3.9 I/O Input (Read) Timing Specification |

|

|

|

|

|

|

|

|

|

|

| ||

|

| Cycle Time Mode: | 250 ns |

| 120 ns | 100 ns | 80 ns | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| IEEE | Min |

| Max | Min | Max | Min | Max | Min | Ma | |

| Item | Symbol |

| x | |||||||||

| Symbol | ns. |

| ns. | ns. | ns. | ns. | ns. | ns. | ||||

|

|

|

| ns. | |||||||||

|

|

|

|

|

|

|

|

|

|

|

| ||

Data Delay after IORD | td(IORD) | tlGLQV |

|

| 100 |

| 50 |

| 50 |

| 45 |

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

Data Hold following IORD | th(IORD) | tlGHQX | 0 |

|

| 5 |

| 5 |

| 5 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

IORD Width Time | tw(IORD) | tlGLIGH | 165 |

|

| 70 |

| 65 |

| 55 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

Address Setup before IORD | tsuA(IORD) | tAVIGL | 70 |

|

| 25 |

| 25 |

| 15 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

Address Hold following IORD | thA(IORD) | tlGHAX | 20 |

|

| 10 |

| 10 |

| 10 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

CE Setup before IORD | tsuCE(IORD) | tELIGL | 5 |

|

| 5 |

| 5 |

| 5 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

CE Hold following IORD | thCE(IORD) | tlGHEH | 20 |

|

| 10 |

| 10 |

| 10 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

REG Setup before IORD | tsuREG (IORD) | tRGLIGL | 5 |

|

| 5 |

| 5 |

| 5 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

REG Hold following IORD | thREG (IORD) | tlGHRGH | 0 |

|

| 0 |

| 0 |

| 0 |

|

| |

|

|

|

|

|

|

|

|

|

|

|

| ||

INPACK Delay Falling from IORD3 | tdfINPACK (IORD) | tlGLIAL | 0 |

| 45 | 0 | na1 | 0 | na1 | 0 | na1 | ||

|

|

|

|

|

|

|

|

|

|

|

| ||

INPACK Delay Rising from IORD3 | tdrINPACK (IORD) | tlGHIAH |

|

| 45 |

| na1 |

| na1 |

| na1 | ||

|

|

|

|

|

|

|

|

|

|

|

| ||

IOIS16 Delay Falling from Address3 | tdfIOIS16 (ADR) | tAVISL |

|

| 35 |

| na1 |

| na1 |

| na1 | ||

|

|

|

|

|

|

|

|

|

|

|

| ||

IOIS16 Delay Rising from Address3 | tdrIOIS16 (ADR) | tAVISH |

|

| 35 |

| na1 |

| na1 |

| na1 | ||

Wait Delay Falling from IORD3 | tdWT(IORD) | tlGLWTL |

|

| 35 |

| 35 |

| 35 |

| na2 | ||

|

|

|

|

|

|

|

|

|

|

|

| ||

Data Delay from Wait Rising3 | td(WT) | tWTHQV |

|

| 0 |

| 0 |

| 0 |

| na2 | ||

|

|

|

|

|

|

|

|

|

|

|

| ||

Wait Width Time3 | tw(WT) | tWTLWTH |

|

| 350 |

| 350 |

| 350 |

| na2 | ||

Transcend Information Inc. | 23 |