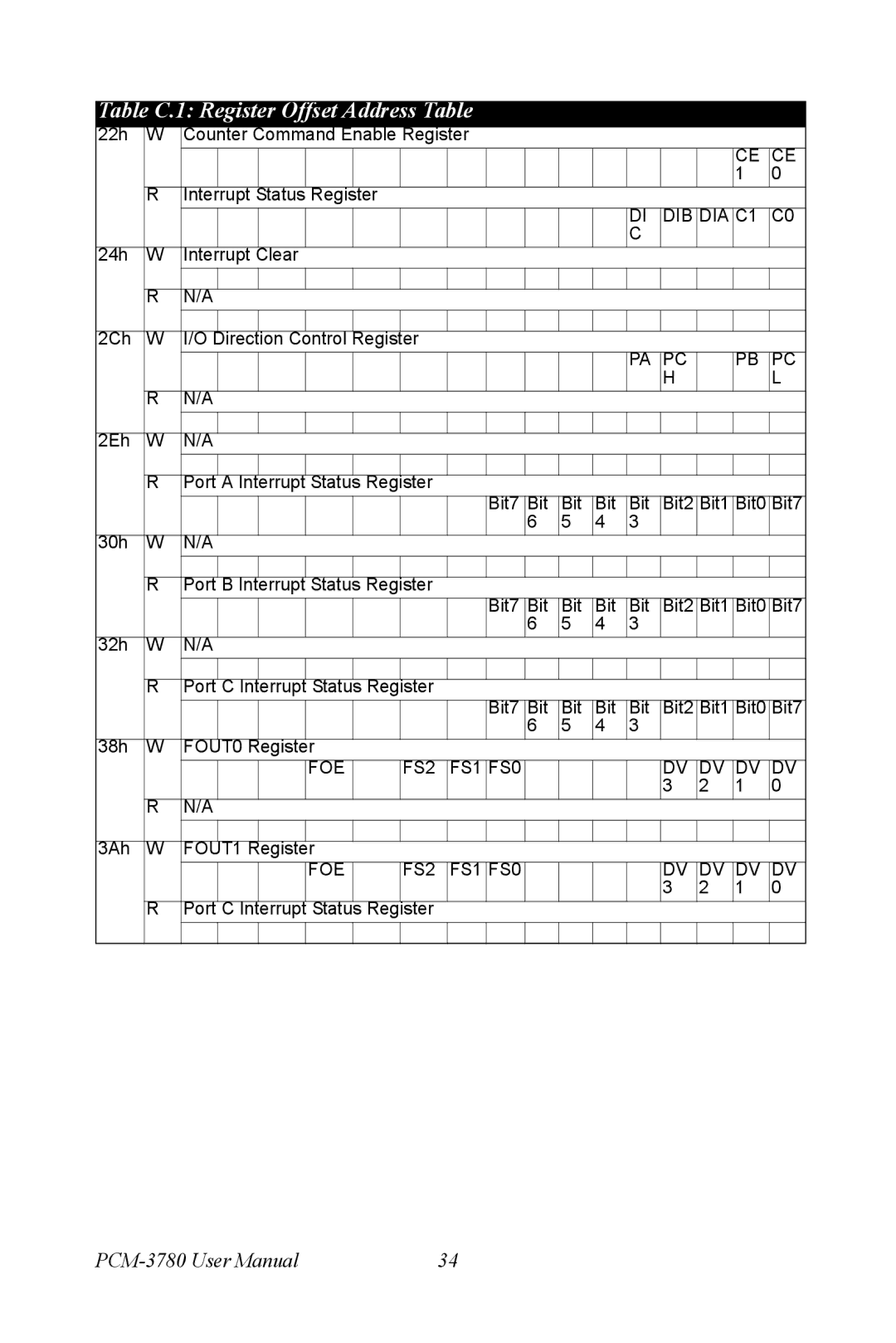

Table C.1: Register Offset Address Table

22h | W | Counter Command Enable Register | CE CE | |

|

|

| ||

| R | Interrupt Status Register | 1 | 0 |

|

|

| ||

|

| DI DIB DIA C1 | C0 | |

|

| C |

|

|

24h | W | Interrupt Clear |

|

|

| R | N/A |

|

|

2Ch | W | I/O Direction Control Register |

|

|

|

| PA PC | PB | PC |

|

| H |

| L |

RN/A 2Eh W N/A

R Port A Interrupt Status Register

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Bit7 | Bit | Bit | Bit | Bit | Bit2 | Bit1 | Bit0 | Bit7 |

|

|

|

|

|

|

|

|

|

| 6 | 5 | 4 | 3 |

|

|

|

|

30h | W | N/A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R | Port | B Interrupt Status Register |

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| Bit7 | Bit | Bit | Bit | Bit | Bit2 | Bit1 | Bit0 | Bit7 |

|

|

|

|

|

|

|

|

|

| 6 | 5 | 4 | 3 |

|

|

|

|

32h | W | N/A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R | Port | C Interrupt Status Register |

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| Bit7 | Bit | Bit | Bit | Bit | Bit2 | Bit1 | Bit0 | Bit7 |

|

|

|

|

|

|

|

|

|

| 6 | 5 | 4 | 3 |

|

|

|

|

38h | W | FOUT0 Register |

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

| FOE |

| FS2 | FS1 | FS0 |

|

|

|

| DV | DV | DV | DV |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 | 2 | 1 | 0 |

| R | N/A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3Ah | W | FOUT1 Register |

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

| FOE |

| FS2 | FS1 | FS0 |

|

|

|

| DV | DV | DV | DV |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 | 2 | 1 | 0 |

| R | Port | C Interrupt Status Register |

|

|

|

|

|

|

|

|

|

| ||||

34 |