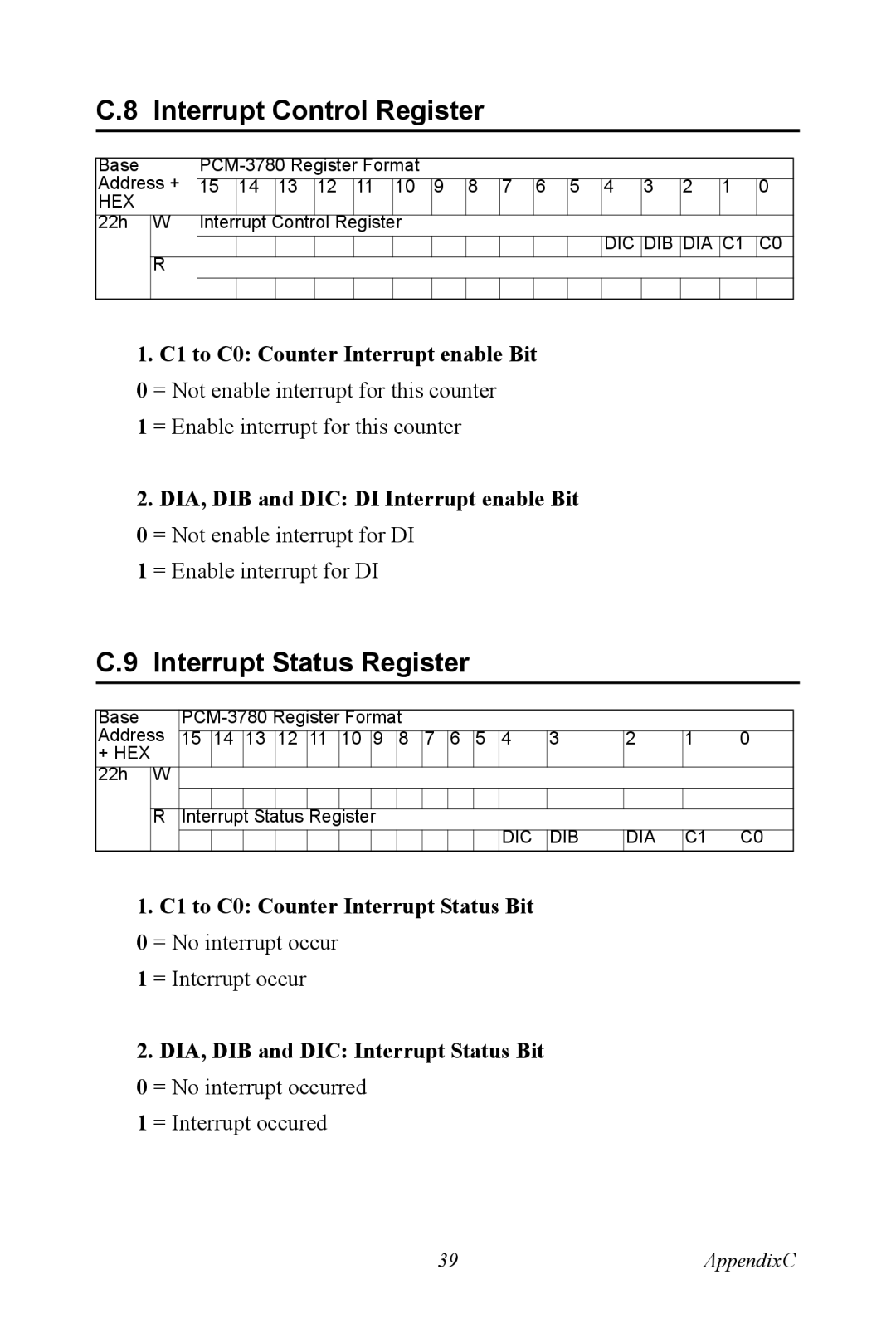

C.8 | Interrupt Control Register |

|

| |||||||||||||||

|

|

|

|

| ||||||||||||||

Base |

|

|

| |||||||||||||||

Address + |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ||

HEX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

22h | W | Interrupt Control Register |

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| DIC | DIB | DIA | C1 | C0 |

|

| R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.C1 to C0: Counter Interrupt enable Bit

0= Not enable interrupt for this counter

1= Enable interrupt for this counter

2.DIA, DIB and DIC: DI Interrupt enable Bit

0= Not enable interrupt for DI

1= Enable interrupt for DI

C.9 | Interrupt Status Register |

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |||||||

Base |

|

|

|

|

|

|

|

|

|

| ||||||||

Address |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ||

+ HEX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

22h | W |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R | Interrupt Status Register |

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| DIC | DIB | DIA | C1 | C0 |

|

1.C1 to C0: Counter Interrupt Status Bit

0= No interrupt occur

1= Interrupt occur

2.DIA, DIB and DIC: Interrupt Status Bit

0= No interrupt occurred

1= Interrupt occured

39 | AppendixC |