User’s Guide

Page

Contents

Contents

Basic Operation

Basic Digital Operation

Optimizing Performance

Custom Arb Waveform Generator

Custom Real Time I/Q Baseband

Awgn Waveform Generator

Contents

Xii

Documentation Overview

Key Reference

PSG Signal Generator Models

Signal Generator Models and Features

E8257D PSG Analog Signal Generator Features

E8267D PSG Vector Signal Generator Features

GPIB/RS-232 LAN LAN Setup

Options Firmware Upgrades

To Upgrade Firmware

Analog Modulation

Swept Signal

Modes of Operation

Continuous Wave

Digital Modulation

Front Panel

Standard E8267D Front Panel Diagram

Amplitude

Display

Softkeys

Knob

Hardkeys in Front Panel Menus Group

Trigger

Help

Numeric Keypad

Mod On/Off

RF On/Off

Hold

Incr Set

Arrow Keys

Contrast Decrease

Preset

Line Power LED

Return

Input

Data

Front Panel Display

Front Panel Display Diagram

Annunciators

Active Entry Area

Frequency Area

Interface

Text Area

Error Message Area

Digital Modulation Annunciators

Amplitude Area

Standard E8267D Rear Panel

Rear Panel

E8267D Option 1EM Rear Panel

Standard E8257D Rear Panel

E8257D Option 1EM Rear Panel

Pattern Trig

Event

Auxiliary I/O

OUT

Digital BUS

GHz REF OUT Serial Prefixes =US4646/MY4646

Bar OUT

ALC Hold Serial Prefixes =US4722/MY4722

AC Power Receptacle

Gpib

MHz EFC

LAN

Auxiliary Interface Connector

MHz

Stop Sweep IN/OUT

MHz OUT

EXT

RF OUT

Pulse Sync OUT

Symbol Sync

LF OUT

Basic Operation

Press Preset Sweep/List Configure List Sweep

Using Table Editors

Modifying Table Items in the Data Fields

Table Editor Softkeys

Setting the RF Output Frequency

Configuring the RF Output

Configuring a Continuous Wave RF Output

Press Frequency 700 MHz More 1 of 3 Freq Ref Set

Setting the Frequency Reference and Frequency Offset

Setting the RF Output Amplitude

Setting the Amplitude Reference and Amplitude Offset

Configuring a Swept RF Output

Using Step Sweep

Activating Scalar Pulse in Sweep Configurations

To Configure a Single Step Sweep

To Edit List Sweep Points

To Configure a Continuous Step Sweep

Using List Sweep

To Configure a Single List Sweep Using Step Sweep Data

Press More 1 of 2 Sweep Trigger Trigger Key

To Configure a Single List Sweep

Press Edit Item 545 MHz

Press Insert Item -2.5 dBm

Using Basic Ramp Sweep Functions

To Configure a Continuous List Sweep

Using Ramp Sweep Option

Equipment Setup

Press Freq Start

Press Frequency Freq CW

Using Markers

Marker Table Editor

Press Turn Off Markers

Press Configure Ramp/Step Sweep

Press Alternate Sweep Off On to On

Using Alternate Sweep

Press Return Sweep Ampl

Configuring a Ramp Sweep for a Master/Slave Setup

Basic Operation Configuring the RF Output

Master/Slave Equipment Setup

Turning On a Modulation Format

Modulating a Signal

Extending the Frequency Range

To Turn RF Output Modulation Off

Applying a Modulation Format to the RF Output

To Turn RF Output Modulation On

Using the Memory Catalog

Using Data Storage Functions

Memory Catalog File Types and Associated Data

Storing Files to the Memory Catalog

Saving an Instrument State

Using the Instrument State Registers

Viewing Stored Files in the Memory Catalog

Deleting a Specific Register within a Sequence

Recalling an Instrument State

Deleting Registers and Sequences

Network Analyzer Save and Recall Functions

Using Security Functions

Deleting All Registers within a Sequence

Deleting All Sequences

Base Instrument Memory

Understanding PSG Memory Types

Base Instrument Memory

Baseband Generator Memory Options 601

Hard Disk Memory

Purpose/Contents Data Input Method Remarks Type Size

Erase and Sanitize All

Removing Sensitive Data from PSG Memory

Erase All

Erase and Overwrite All

Setting the Secure Mode Level

Using the Secure Mode

Hard Disk

Activating the Secure Mode

Processor Board

Enabling a Software Option

Using the Secure Display

Enabling Options

Proceed With Reconfiguration Confirm Change

Using the Web Server

Activating the Web Server

Perform the following steps to access the Web Server

Signal Generator Web

Web Page Front Panel

Custom Modulation

Basic Digital Operation

Custom Real Time I/Q Baseband

Arbitrary ARB Waveform File Headers

Custom Arb Waveform Generator

Creating a File Header for a Modulation Format Waveform

Modifying Header Information in a Modulation Format

Press ARB Setup Header Utilities

Description key, see 2 on

Custom Digital Modulation Default Header Display

Also shows the softkey paths used in steps four through nine

ARB Setup Softkey Menu and Marker Utilities

Saved File Header Changes

Modifying Header Information

Press Mode Dual ARB Select Waveform

Viewing Header Information with the Dual ARB Player Off

Press Return Header Utilities

Viewing Header Information for a Different Waveform File

Seq

Playing a Waveform File that Contains a Header

Waveform is selected saved header settings are applied

Press Mode Dual ARB

Using the Dual ARB Waveform Player

Accessing the Dual ARB Player

Creating Waveform Segments

Press Done Inserting

Press Mode Dual ARB Waveform Segments Load Store to Store

Building and Storing a Waveform Sequence

Press Rename Segment Editing Keys Clear Text

Press Edit Repetitions 200 Enter

Playing a Waveform

Editing a Waveform Sequence

Adding Real-Time Noise to a Dual ARB Waveform

Storing Waveform Segments to Non-volatile Memory

Configuring Awgn

Storing and Loading Waveform Segments

Press Load All From Nvwfm Memory

Using Waveform Markers

Renaming a Waveform Segment

Loading Waveform Segments from Non-volatile Memory

Positive Marker File Bit N

Waveform Marker Concepts

Marker File Generation

Marker Point Edit Requirements

Saving Marker Polarity and Routing Settings

Example of Correct Use

Accessing Marker Utilities

Viewing Waveform Segment Markers

Highlight the desired marker number Press Marker 1 2 3

Clearing Marker Points from a Waveform Segment

Clearing All Marker Points

Placing a Marker Across a Range of Points

Setting Marker Points in a Waveform Segment

Clearing a Range of Marker Points

Clearing a Single Marker Point

Placing Repetitively Spaced Markers

Placing a Marker on a Single Point

As You Create a Waveform Sequence

Controlling Markers in a Waveform Sequence Dual ARB Only

Press Return Name And Store Enter

An Existing Waveform Sequence

Viewing a Marker Pulse

Using the RF Blanking Marker Function

RF Signal

Marker Utilities menu page 92, press Marker Polarity

Setting Marker Polarity

Triggering Waveforms

Source

Mode and Response

Accessing Trigger Utilities

Continuous, Single, or Segment Advance Modes

Setting the Polarity of an External Trigger

Using Gated Triggering

Gated Mode

Press Trigger Gated

Press Select Waveform

Press Trigger Source Trigger Key

Using Segment Advance Triggering

Press Trigger Segment Advance

How Power Peaks Develop

Using Waveform Clipping

Chapter 109

How Peaks Cause Spectral Regrowth

How Clipping Reduces Peak-to-Average Power

Circular Clipping

Chapter 113

Configuring Circular Clipping

Press Clip I To 80 %

Configuring Rectangular Clipping

Press Return Return Clipping

How DAC Over-Range Errors Occur

Using Waveform Scaling

See

How Scaling Eliminates DAC Over-Range Errors

Scaling a Waveform File in Volatile Memory

Scaling a Currently Playing Waveform Runtime Scaling

Yes ARB On

Using the ALC

Selecting ALC Bandwidth

To Select an ALC Bandwidth

Connect the Equipment

Using External Leveling

To Level with Detectors and Couplers/Splitters

Required Equipment

Determining the Leveled Output Power

Configure the Signal Generator

External Leveling with Option 1E1 Signal Generators

Press Amplitude Set Atten 45 dB Press Set ALC Level 5 dBm

Creating and Applying User Flatness Correction

To Level with a mm-Wave Source Module

Creating a User Flatness Correction Array

Configure the Power Meter

Press Freq Start 1 GHz Press Freq Stop 10 GHz

Press Configure Step Array

Press Amplitude More 1 of 2 Ampl Offset

Perform the User Flatness Correction

Performing the User Flatness Correction Manually

Press # of Points 10 Enter

Press Return Return Flatness Off On to On

Press More 1 of 2 User Flatness Configure Cal Array

Recalling and Applying a User Flatness Correction Array

Press Load/Store Press Store to File

Press Return Flatness Off On to On

Returning the Signal Generator to Gpib Listener Mode

Press Load From Selected File Confirm Load From File

Chapter 129

130 Chapter

Chapter 131

Press Amplitude 0 dBm Press RF On/Off

Press Return Return Flatness Off On

Applying the User Flatness Correction Array

To Select the Reference Oscillator Bandwidth

Adjusting Reference Oscillator Bandwidth Option UNR/UNX

When using the internal timebase reference

When using an external timebase reference

Internal Timebase 125 Hz External Timebase 25 Hz

To Restore Factory Default Settings

136 Chapter

Analog Modulation Waveforms

Analog Modulation

Configuring FM Option UNT

Configuring AM Option UNT

DC Offset and External FM

Configuring ΦM Option UNT

To Activate FM

To Set the ΦM Deviation and Rate

To Activate Pulse Modulation

Configuring Pulse Modulation Option UNU/UNW

To Activate ΦM

To Set the Pulse Period, Width, and Triggering

Press FM Dev 75 kHz Press FM Rate 10 kHz

Configuring the LF Output Option UNT

Configuring the Internal Modulation as the LF Output Source

Configuring the Waveform

To Configure the LF Output with a Function Generator Source

Configuring the Low Frequency Output

Configuring the Function Generator as the LF Output Source

Overview

Working with Predefined Setups Modes

Custom Digital Mod State

Working with User-Defined Setups Modes−Custom Arb Only

Modifying a Single-Carrier Nadc Setup

Press Mode Custom Arb Waveform Generator Setup Select

Press Return Digital Modulation Off On

Customizing a Multicarrier Setup

Enter

Working with Filters

Recalling a User-Defined Custom Digital Modulation State

Filter Select Gaussian

Using a Predefined FIR Filter

Selecting a Predefined FIR Filter

Filter Filter Alpha

Restoring Default FIR Filter Parameters

Using a User-Defined FIR Filter

Press Load/Store Store To File

Press Display Impulse Response

150 Chpater

Press Mirror Table

Press Return Load/Store Store To File

Press Return Display Impulse Response

To Set a Symbol Rate

Working with Symbol Rates

To Restore the Default Symbol Rate Custom Real Time I/Q Only

To Select a Predefined Modulation Type

Working with Modulation Types

Press More 2 of 2 Display I/Q Map

To Use a User-Defined Modulation Type Real Time I/Q Only

Editing Keys Clear Text

Press More 1 of 2 Load/Store Store To File

Symbol Data Value

Press .235702 Enter, then .235702 Enter

Press More 2

Edit Keys Clear Text

Press I/Q Path Wide Ext Rear Inputs

Differential Wideband IQ Option

Single-Ended Wideband IQ Option 015 Dis

Press Mode Custom Arb Waveform Generator

Configuring Hardware

To Set the ARB Reference

Setting for an External or Internal Reference

Setting the External Frequency

Press Ext Delay Time 100 msec

Custom Arb Waveform Generator Configuring Hardware

Custom Real Time I/Q Baseband

Selecting a Predefined Real Time Modulation Setup

Working with Data Patterns

Deselecting a Predefined Real Time Modulation Setup

Selecting a Predefined Fixed 4-bit Data Pattern

Using a Predefined Data Pattern

Using a User-Defined Data Pattern

Selecting a Predefined PN Sequence Data Pattern

168 Chapter

Press Edit File

Press Mode Custom Real Time I/Q Baseband Data User File

Modifying an Existing Data Pattern User File

Press More 1 of 2 Rename Editing Keys Clear Text

Press Goto 4 C Enter

Press Mode Custom Real Time I/Q Baseband Data Ext

Using an Externally Supplied Data Pattern

To Apply Bit Errors to an Existing Data Pattern User File

Press Apply Bit Errors Press Bit Errors 5 Enter

Using User-Defined Burst Shape Curves

Configuring the Burst Rise and Fall Parameters

To Create and Store User-Defined Burst Shape Curves

Press More 1 of 2 Display Burst Shape

Press Return Custom Off On

To Set the BBG Reference

Press Select File

Press Ext BBG Ref Freq

To Adjust the I/Q Scaling

To Set the BBG Data Clock to External or Internal

Understanding Differential Encoding

Working with Phase Polarity

To Set Phase Polarity to Normal or Inverted

Working with Differential Data Encoding

Differential Data Encoding

How Differential Encoding Works

Transmittedbiti= databiti 1 ⊕ databiti

Example

1st

Using Differential Encoding

1st Symbol 5th Symbol

Map QAM 4QAM

Configuring User-Defined I/Q Modulation

Accessing the Differential State Map Editor

Press Configure Differential Encoding

Editing the Differential State Map

Press Return Differential Encoding Off On

Multitone Waveform Generator

Press Multitone Off On to On

Creating, Viewing, and Optimizing Multitone Waveforms

To Create a Custom Multitone Waveform

To View a Multitone Waveform

To Edit the Multitone Setup Table

Press Apply Multitone

Intermodulation Carrier Distortion

To Minimize Carrier Feedthrough

Tone Carrier

Tone Minimized Carrier

To Determine Peak to Average Characteristics

Ccdf Plot with Fixed Phase Set

Peak Power

Ccdf Plot with Random Phase Set

194 Chapter

Creating, Viewing, and Modifying Two-Tone Waveforms

Two-Tone Waveform Generator

To Create a Two-Tone Waveform

To View a Two-Tone Waveform

Carrier Feedthrough Distortion

Two-Tone Channels Intermodulation Carrier Distortion

Main Marker Minimized Carrier Feedthrough Delta Marker

To Change the Alignment of a Two-Tone Waveform

Intermodulation Distortion Carrier Frequency

Two-Tone

Frequency

Arb Waveform Generator Awgn

Configuring the Awgn Generator

Configuring the RF Output

Generating the Waveform

Real Time I/Q Baseband Awgn

Clock and Sample Rates

N5102A Digital Signal Interface Module

Clock Timing

Least significant bit Most significant bit

Data Setup Menu for a Parallel Port Configuration

Maximum Clock Rates

Input Serial Clock Rates

Serial Port Configuration Clock Rates

Output Serial Clock Rates

Input Parallel and Parallel Interleaved Clock Rates

Output Parallel and Parallel Interleaved Clock Rates

Common Frequency Reference

Clock Source

Baseband GEN REF

PSG Frequency Reference Connections

Internally Generated Clock Device DUT Supplied Clock

Clock Timing for Parallel Data

Clock Per Sample

Clocks Per Sample

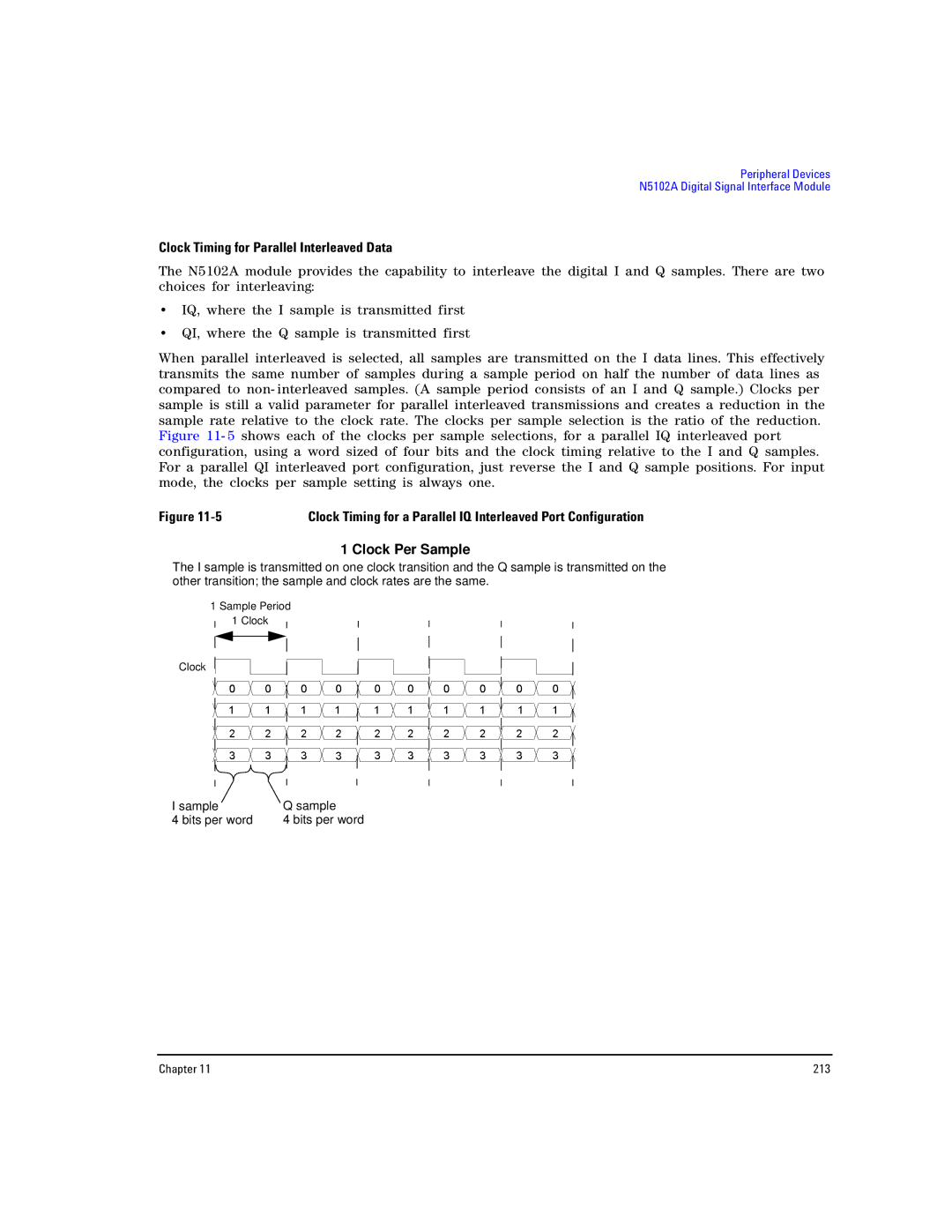

Clock Timing for Parallel Interleaved Data

214 Chapter

Clock Timing for Serial Data

Clock Timing for Phase and Skew Adjustments

Connecting the Clock Source and the Device Under Test

Clock to the device is in the ribbon

Data Types

Output Mode

Input Mode

Maximum Sample Rate for Selected Filter

Operating the N5102A Module in Output Mode

Setting up the Signal Generator Baseband Data

Accessing the N5102A Module User Interface

First-Level Softkey Menu

Selecting the Data Parameters

Selecting the Output Direction

Data Setup Menu Location

Chapter 223

Press the Gain, Offset & Scaling softkey

Configuring the Clock Signal

Chapter 225

Clocks Per Sample softkey

If External or Device is Selected

Clock Source Settings and Connectors

Generating Digital Data

Operating the N5102A Module in Input Mode

Selecting the Input Direction

230 Chapter

Press the Clock Setup softkey, as shown

232 Chapter

Chapter 233

234 Chapter

Chapter 235

Digital Data

Using Agilent Millimeter-Wave Source Modules

Millimeter-Wave Source Modules

Setting Up the External Source Module

Setup for E8257D PSG without Option 1EA

Turn on the signal generator’s line power

Configuring the Signal Generator

Using Other Source Modules

Chapter 241

Toggle the OEM Source Off On softkey to On

No RF Output Power when Playing a Waveform File

RF Output Power Problems

Amplitude More 1 of 2 Ampl Offset 0 dB

RF Output Power too Low

Power Supply has Shut Down

Signal Loss While Working with a Mixer

Mixer

Effects of Reverse Power on ALC

Setting ALC Off Mode

Signal Loss While Working with a Spectrum Analyzer

Reverse Power Solution

No Modulation at the RF Output

Setting Power Search Mode

Press Do Power Search

Incorrect List Sweep Dwell Time

Sweep Problems

Cannot Turn Off Sweep Mode

Sweep Appears to be Stalled

Press Recall 99 Enter

Data Storage Problems

Press Configure Step Sweep

List Sweep Information is Missing from a Recalled Register

Press Utility Instrument Info/Help Mode

Cannot Turn Off Help Mode

Signal Generator Locks Up

Fail-Safe Recovery Sequence

Characteristic Front Panel Display Error Queue

Error Messages

Error Message Types

Error Message File

Error Message Format

Returning a Signal Generator to Agilent Technologies

Contacting Agilent Sales and Service Offices

254 Chapter

Index

Awgn ARB

Custom 143-163,165-184 formats

FAQ

Auxiliary Interface 27 Gpib

260 Index

Index 261

262 Index

Scpi

264 Index

Index 265

266 Index