Preliminary Information

AMD Athlon™ XP Processor Model 10 Data Sheet | 26237C— May 2003 |

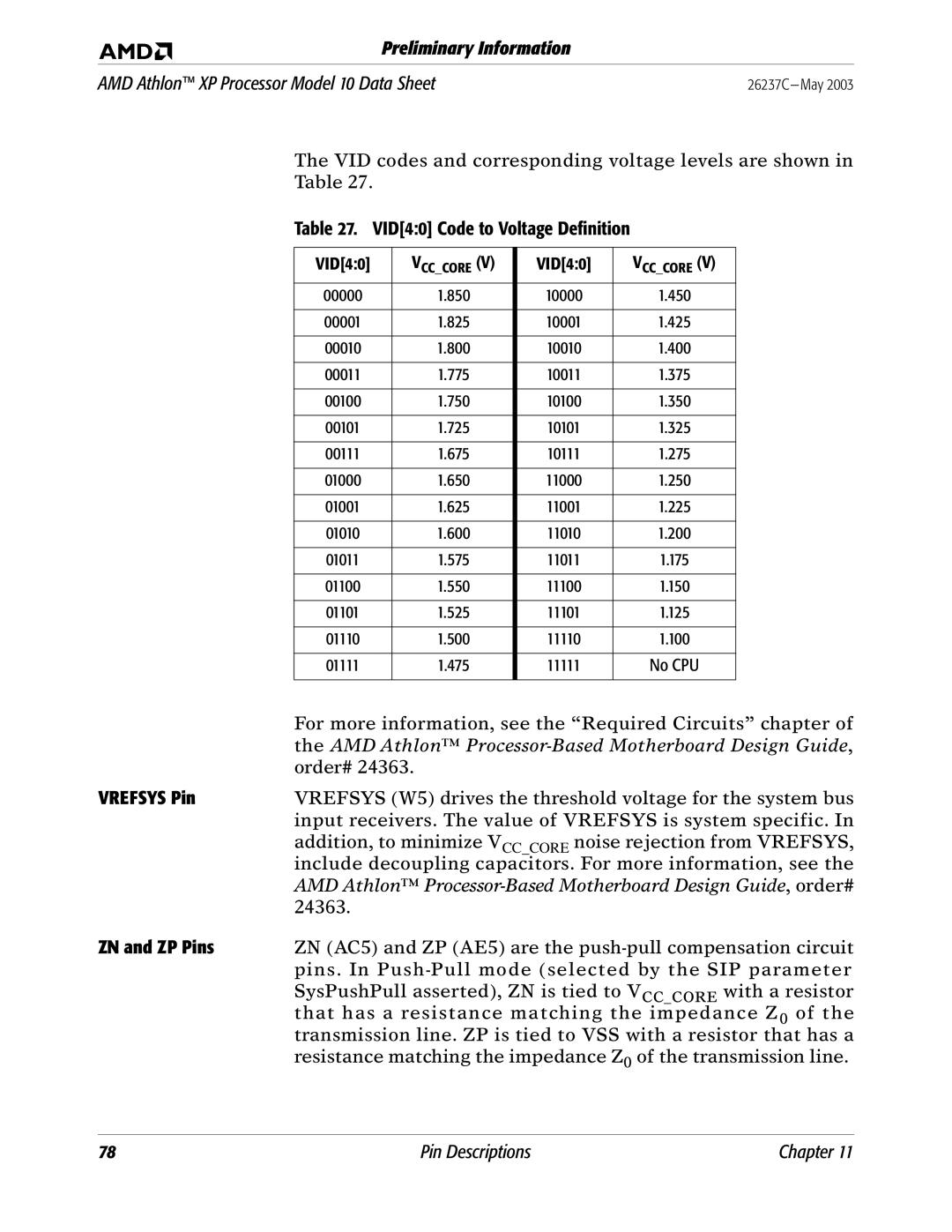

The VID codes and corresponding voltage levels are shown in

Table 27.

Table 27. VID[4:0] Code to Voltage Definition

VID[4:0] | VCC_CORE (V) | VID[4:0] | VCC_CORE (V) |

00000 | 1.850 | 10000 | 1.450 |

|

|

|

|

00001 | 1.825 | 10001 | 1.425 |

|

|

|

|

00010 | 1.800 | 10010 | 1.400 |

|

|

|

|

00011 | 1.775 | 10011 | 1.375 |

|

|

|

|

00100 | 1.750 | 10100 | 1.350 |

|

|

|

|

00101 | 1.725 | 10101 | 1.325 |

|

|

|

|

00111 | 1.675 | 10111 | 1.275 |

|

|

|

|

01000 | 1.650 | 11000 | 1.250 |

|

|

|

|

01001 | 1.625 | 11001 | 1.225 |

|

|

|

|

01010 | 1.600 | 11010 | 1.200 |

|

|

|

|

01011 | 1.575 | 11011 | 1.175 |

|

|

|

|

01100 | 1.550 | 11100 | 1.150 |

|

|

|

|

01101 | 1.525 | 11101 | 1.125 |

|

|

|

|

01110 | 1.500 | 11110 | 1.100 |

|

|

|

|

01111 | 1.475 | 11111 | No CPU |

|

|

|

|

| For more information, see the “Required Circuits” chapter of |

| the AMD Athlon™ |

| order# 24363. |

VREFSYS Pin | VREFSYS (W5) drives the threshold voltage for the system bus |

| input receivers. The value of VREFSYS is system specific. In |

| addition, to minimize VCC_CORE noise rejection from VREFSYS, |

| include decoupling capacitors. For more information, see the |

| AMD Athlon™ |

| 24363. |

ZN and ZP Pins | ZN (AC5) and ZP (AE5) are the |

| pins. In |

| SysPushPull asserted), ZN is tied to VCC_CORE with a resistor |

| that has a resistance matching the impedance Z0 of the |

| transmission line. ZP is tied to VSS with a resistor that has a |

| resistance matching the impedance Z0 of the transmission line. |

78 | Pin Descriptions | Chapter 11 |