Preliminary Information

AMD Athlon™ XP Processor Model 10 Data Sheet | 26237C— May 2003 |

6.2Advanced 333 FSB AMD Athlon™ XP Processor Model 10 SYSCLK and SYSCLK# AC Characteristics

Table 2 shows the SYSCLK/SYSCLK# differential clock AC characteristics of this processor.

Table 2. | Advanced 333 FSB SYSCLK and SYSCLK# AC Characteristics |

|

| |||

|

|

|

|

|

|

|

Symbol |

| Parameter Description | Minimum | Maximum | Units | Notes |

|

|

|

|

|

|

|

|

| Clock Frequency | 50 | 166 | MHz | 1 |

|

|

|

|

|

|

|

|

| Duty Cycle | 30% | 70% |

|

|

|

|

|

|

|

|

|

t1 |

| Period | 6 |

| ns | 2, 3 |

t2 |

| High Time | 1.0 |

| ns |

|

t3 |

| Low Time | 1.0 |

| ns |

|

t4 |

| Fall Time |

| 2 | ns |

|

t5 |

| Rise Time |

| 2 | ns |

|

|

| Period Stability |

| ± 300 | ps |

|

|

|

|

|

|

|

|

Notes: |

|

|

|

|

|

|

1. The AMD Athlon™ system bus operates at twice this clock frequency. |

|

|

| |||

2. Circuitry driving the AMD Athlon system bus clock inputs must exhibit a suitably low | ||||||

to track the jitter. The |

| |||||

3. Circuitry driving the AMD Athlon system bus clock inputs may purposely alter the AMD Athlon system bus clock frequency (spread | ||||||

spectrum clock generators). In no cases can the AMD Athlon system bus period violate the minimum specification above. | ||||||

AMD Athlon system bus clock inputs can vary from 100% of the specified frequency to 99% of the specified frequency at a | ||||||

maximum rate of 100 kHz. |

|

|

|

| ||

|

|

|

|

|

|

|

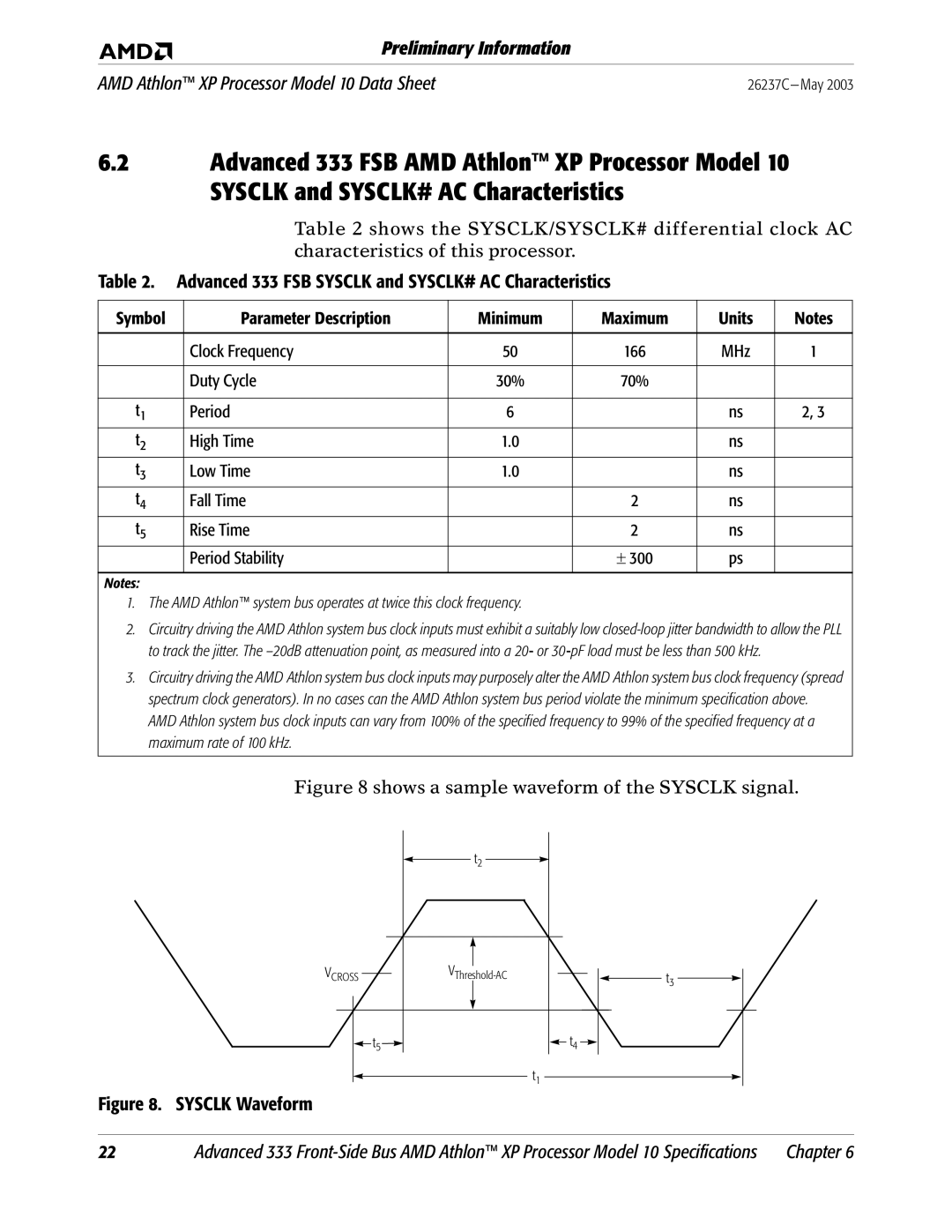

Figure 8 shows a sample waveform of the SYSCLK signal.

| t2 |

|

VCROSS | t3 | |

| t | t4 |

| 5 |

|

|

| t1 |

Figure 8. SYSCLK Waveform

22 | Advanced 333 | Chapter 6 |