Preliminary Information

26237C | AMD Athlon™ XP Processor Model 10 Data Sheet |

8 Electrical Data

This chapter describes the electrical characteristics that apply to all desktop AMD Athlon™ XP processors model 10.

8.1Conventions

The conventions used in this chapter are as follows:

■Current specified as being sourced by the processor is negative.

■Current specified as being sunk by the processor is positive.

8.2Interface Signal Groupings

The electrical data in this chapter is presented separately for each signal group.

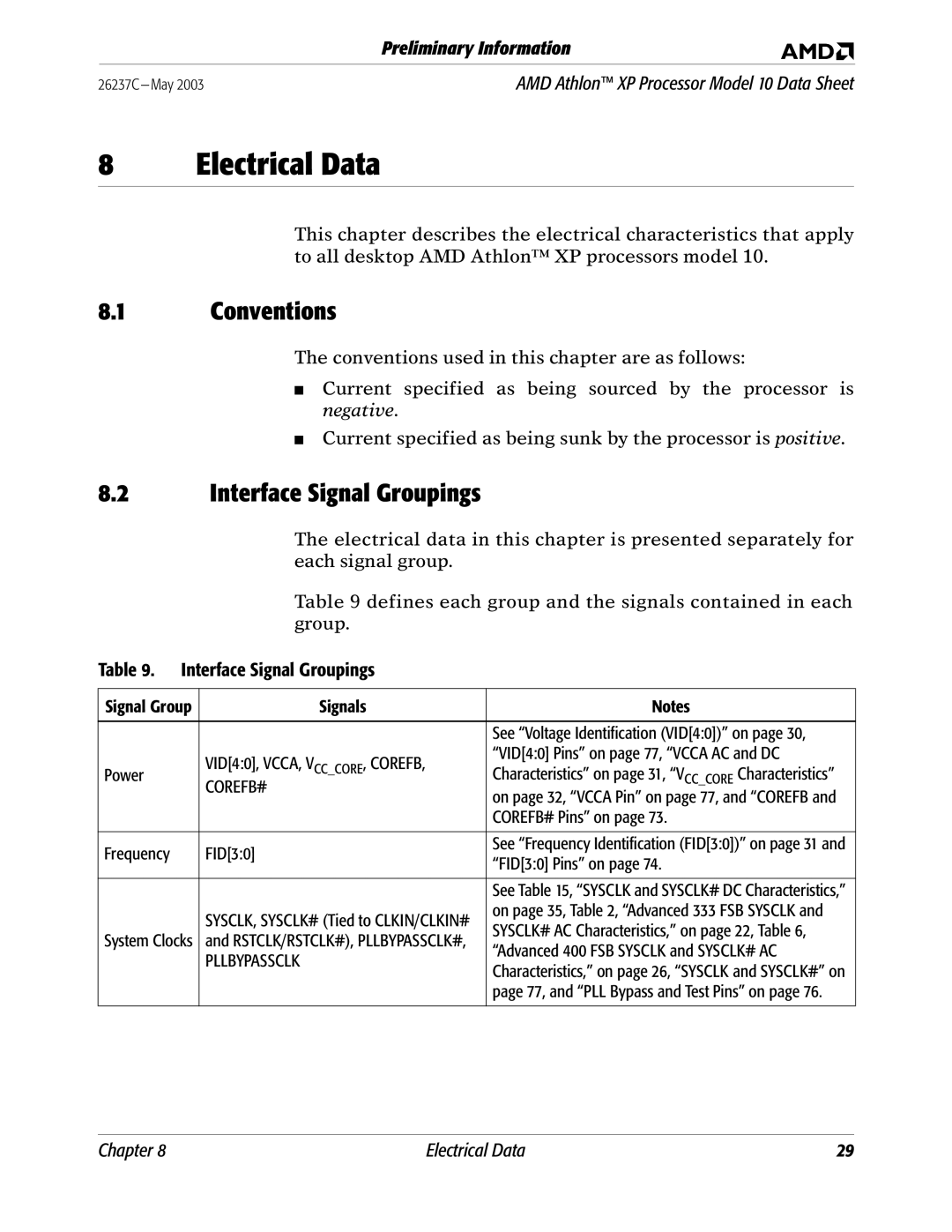

Table 9 defines each group and the signals contained in each group.

Table 9. | Interface Signal Groupings |

| ||

|

|

| ||

Signal Group | Signals | Notes | ||

|

|

|

| |

|

|

| See “Voltage Identification (VID[4:0])” on page 30, | |

|

| VID[4:0], VCCA, VCC_CORE, COREFB, | “VID[4:0] Pins” on page 77, “VCCA AC and DC | |

Power |

| Characteristics” on page 31, “VCC_CORE Characteristics” | ||

| COREFB# | |||

|

| on page 32, “VCCA Pin” on page 77, and “COREFB and | ||

|

|

| ||

|

|

| COREFB# Pins” on page 73. | |

|

|

|

| |

Frequency |

| FID[3:0] | See “Frequency Identification (FID[3:0])” on page 31 and | |

| “FID[3:0] Pins” on page 74. | |||

|

|

| ||

|

|

|

| |

|

|

| See Table 15, “SYSCLK and SYSCLK# DC Characteristics,” | |

|

| SYSCLK, SYSCLK# (Tied to CLKIN/CLKIN# | on page 35, Table 2, “Advanced 333 FSB SYSCLK and | |

|

| SYSCLK# AC Characteristics,” on page 22, Table 6, | ||

System Clocks | and RSTCLK/RSTCLK#), PLLBYPASSCLK#, | |||

“Advanced 400 FSB SYSCLK and SYSCLK# AC | ||||

|

| PLLBYPASSCLK | ||

|

| Characteristics,” on page 26, “SYSCLK and SYSCLK#” on | ||

|

|

| ||

|

|

| page 77, and “PLL Bypass and Test Pins” on page 76. | |

|

|

|

| |

Chapter 8 | Electrical Data | 29 |