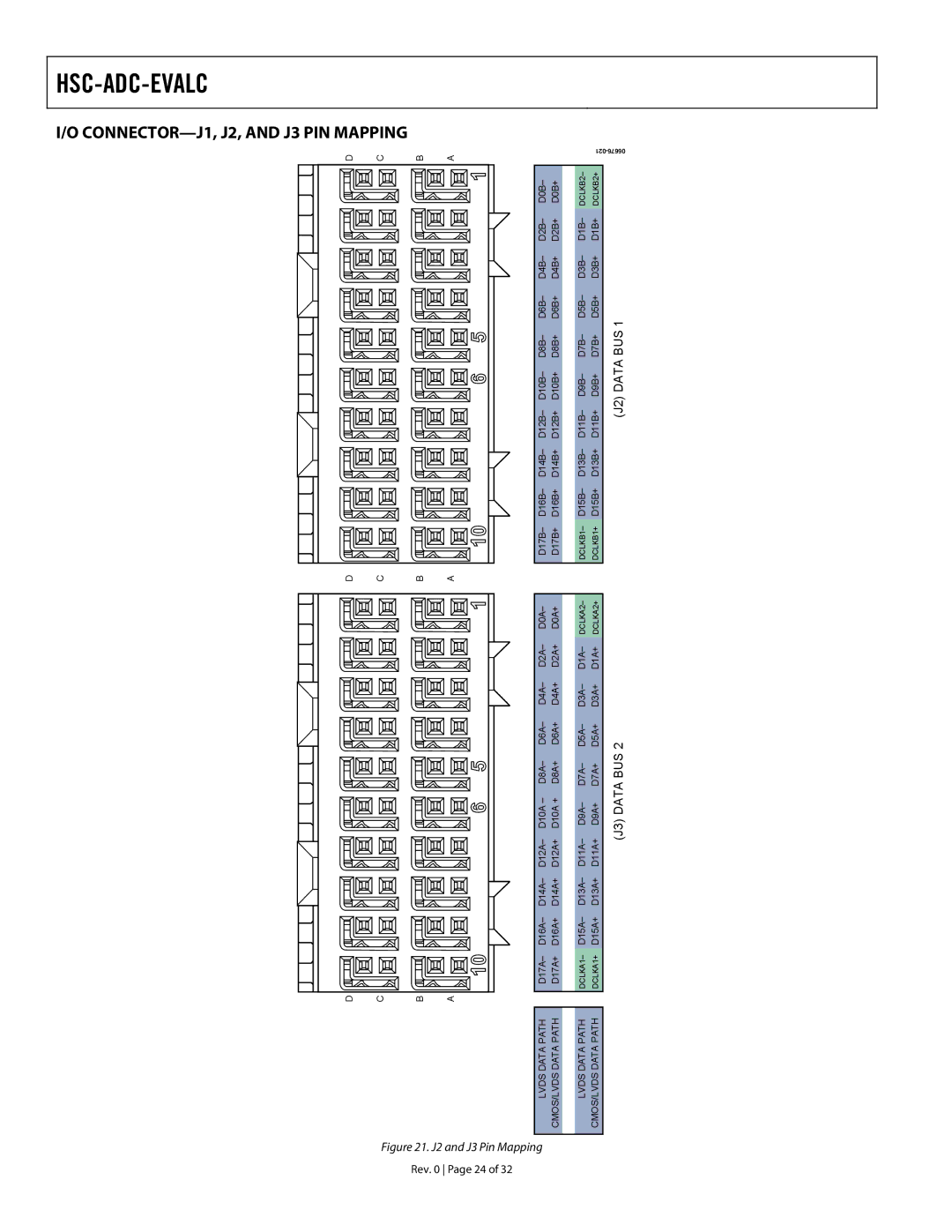

Rev. | Figure 21. |

0 Page 24 of 32 | J2 and J3 PinMapping |

D | D |

C | C |

B | B |

A | A |

| I/O |

|

| J2, AND J3 PIN |

|

D | MAPPING |

|

C |

| |

B |

| |

|

| |

A |

|

|

LVDS DATA PATH > CMOS/LVDS DATA PATH >

LVDS DATA PATH > CMOS/LVDS DATA PATH >

D17A– | D16A– D14A– | D12A– | D10A– | D8A– | D6A– | D4A– | D2A– | D0A– | ||

D17A+ | D16A+ D14A+ | D12A+ | D10A+ | D8A+ | D6A+ | D4A+ | D2A+ | D0A+ | ||

|

|

|

|

|

|

|

|

|

|

|

DCLKA1– | D15A– | D13A– | D11A– |

| D9A– | D7A– | D5A– | D3A– | D1A– | DCLKA2– |

DCLKA1+ | D15A+ | D13A+ | D11A+ | D9A+ | D7A+ | D5A+ | D3A+ | D1A+ | DCLKA2+ | |

|

|

|

|

|

|

|

|

|

|

|

(J3) DATA BUS 2

D17B– | D16B– | D14B– | D12B– | D10B– | D8B– | D6B– | D4B– | D2B– | D0B– | |

D17B+ | D16B+ | D14B+ | D12B+ | D10B+ | D8B+ | D6B+ | D4B+ | D2B+ | D0B+ | |

|

|

|

|

|

|

|

|

|

|

|

DCLKB1– | D15B– | D13B– | D11B– | D9B– | D7B– | D5B– | D3B– | D1B– | DCLKB2– |

|

DCLKB1+ | D15B+ | D13B+ | D11B+ | D9B+ | D7B+ | D5B+ | D3B+ | D1B+ | DCLKB2+ | |

|

|

| (J2) DATA BUS 1 |

|

|

|

| |||