HSC-ADC-EVALC

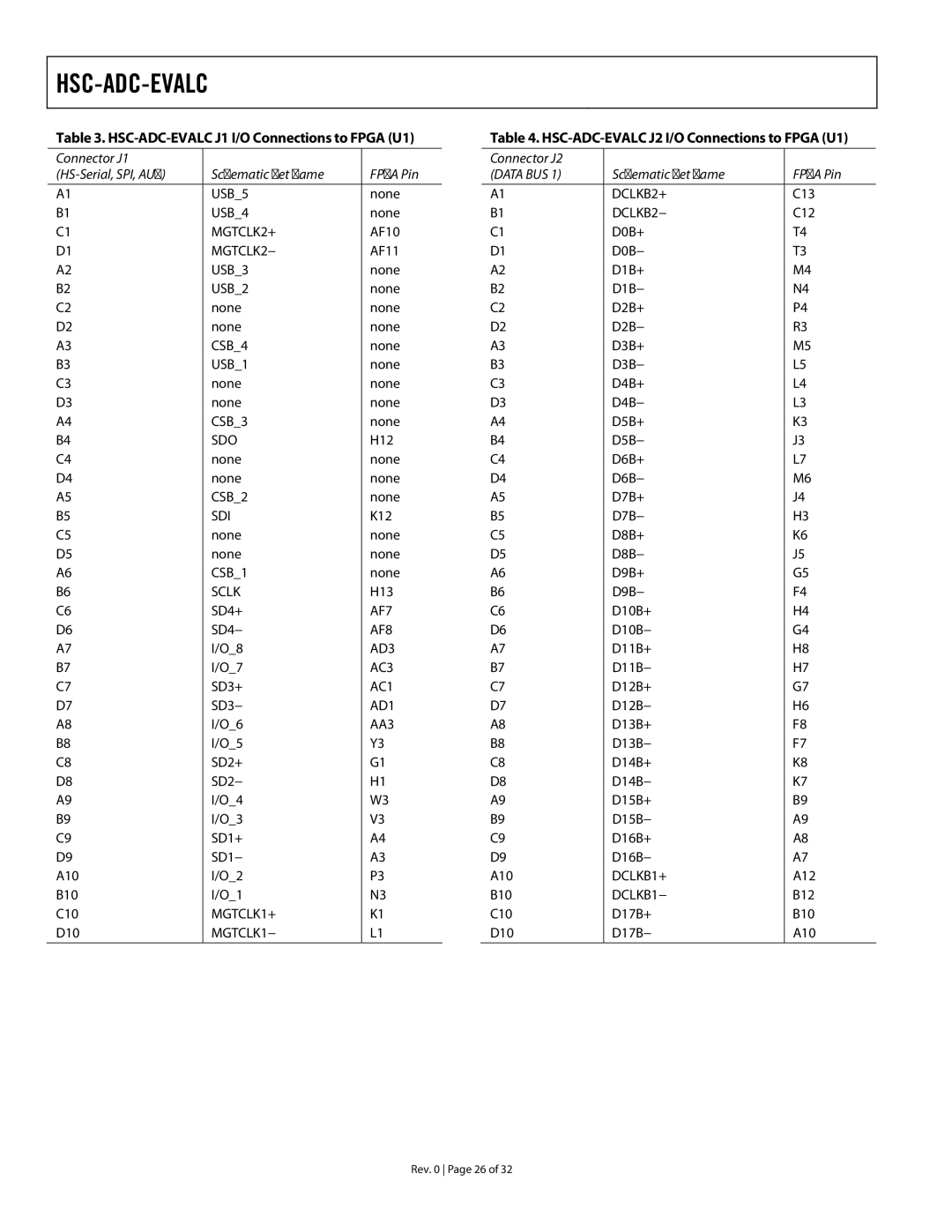

Table 3. HSC-ADC-EVALC J1 I/O Connections to FPGA (U1)

Connector J1 |

|

|

Schematic Net Name | FPGA Pin | |

|

|

|

A1 | USB_5 | none |

B1 | USB_4 | none |

C1 | MGTCLK2+ | AF10 |

D1 | MGTCLK2− | AF11 |

A2 | USB_3 | none |

B2 | USB_2 | none |

C2 | none | none |

D2 | none | none |

A3 | CSB_4 | none |

B3 | USB_1 | none |

C3 | none | none |

D3 | none | none |

A4 | CSB_3 | none |

B4 | SDO | H12 |

C4 | none | none |

D4 | none | none |

A5 | CSB_2 | none |

B5 | SDI | K12 |

C5 | none | none |

D5 | none | none |

A6 | CSB_1 | none |

B6 | SCLK | H13 |

C6 | SD4+ | AF7 |

D6 | SD4− | AF8 |

A7 | I/O_8 | AD3 |

B7 | I/O_7 | AC3 |

C7 | SD3+ | AC1 |

D7 | SD3− | AD1 |

A8 | I/O_6 | AA3 |

B8 | I/O_5 | Y3 |

C8 | SD2+ | G1 |

D8 | SD2− | H1 |

A9 | I/O_4 | W3 |

B9 | I/O_3 | V3 |

C9 | SD1+ | A4 |

D9 | SD1− | A3 |

A10 | I/O_2 | P3 |

B10 | I/O_1 | N3 |

C10 | MGTCLK1+ | K1 |

D10 | MGTCLK1− | L1 |

|

|

|

Table 4. HSC-ADC-EVALC J2 I/O Connections to FPGA (U1)

Connector J2 |

|

|

(DATA BUS 1) | Schematic Net Name | FPGA Pin |

|

|

|

A1 | DCLKB2+ | C13 |

B1 | DCLKB2− | C12 |

C1 | D0B+ | T4 |

D1 | D0B− | T3 |

A2 | D1B+ | M4 |

B2 | D1B− | N4 |

C2 | D2B+ | P4 |

D2 | D2B− | R3 |

A3 | D3B+ | M5 |

B3 | D3B− | L5 |

C3 | D4B+ | L4 |

D3 | D4B− | L3 |

A4 | D5B+ | K3 |

B4 | D5B− | J3 |

C4 | D6B+ | L7 |

D4 | D6B− | M6 |

A5 | D7B+ | J4 |

B5 | D7B− | H3 |

C5 | D8B+ | K6 |

D5 | D8B− | J5 |

A6 | D9B+ | G5 |

B6 | D9B− | F4 |

C6 | D10B+ | H4 |

D6 | D10B− | G4 |

A7 | D11B+ | H8 |

B7 | D11B− | H7 |

C7 | D12B+ | G7 |

D7 | D12B− | H6 |

A8 | D13B+ | F8 |

B8 | D13B− | F7 |

C8 | D14B+ | K8 |

D8 | D14B− | K7 |

A9 | D15B+ | B9 |

B9 | D15B− | A9 |

C9 | D16B+ | A8 |

D9 | D16B− | A7 |

A10 | DCLKB1+ | A12 |

B10 | DCLKB1− | B12 |

C10 | D17B+ | B10 |

D10 | D17B− | A10 |

|

|

|

Rev. 0 Page 26 of 32