HSC-ADC-EVALC

| WALL OUTLET |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| ONBOARD POWER | ||||||||

| 100V TO 240V AC |

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SUPPLY | ||||||

| 47Hz TO 63Hz |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

| 5V DC |

|

|

| – | + |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

| SWITCHING |

|

|

| 3A MAX |

|

|

|

|

|

| |||||||

|

|

|

|

| POWER |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GND | V | ||||

|

|

|

|

| SUPPLY |

|

|

|

| DATA BUS 2 |

|

|

|

|

|

|

| REG | |||

|

|

|

|

|

|

|

|

|

|

|

| PARALLEL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| LVDS/CMOS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| OUTPUTS |

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| EVALUATION |

|

|

|

| DATA CAPTURE | |||||

| ROHDE & SCHWARZ, |

|

|

|

|

|

| BOARD |

|

|

|

|

|

| BOARD | ||||||

|

| SMHU, |

|

|

| XFMR |

|

|

|

|

|

|

|

|

|

| |||||

| 2V |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

| FILTER |

| INPUT | DATA BUS 1 |

|

|

|

|

|

|

|

|

| |||||

| SYNTHESIZER |

|

|

|

|

|

|

|

|

|

|

|

| USB | |||||||

|

|

|

|

|

|

|

| PARALLEL |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| ROHDE & SCHWARZ, |

|

|

|

|

|

| LVDS/CMOS |

|

|

|

|

|

| CONNECTION | ||||||

|

|

|

|

| CLK | OUTPUTS |

|

|

|

|

|

|

|

|

| ||||||

|

| SMHU, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| 2V |

|

|

|

|

|

|

| SPI |

|

|

|

|

| SPI |

|

| ||||

| SYNTHESIZER |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

PC

RUNNING

VisualAnalog

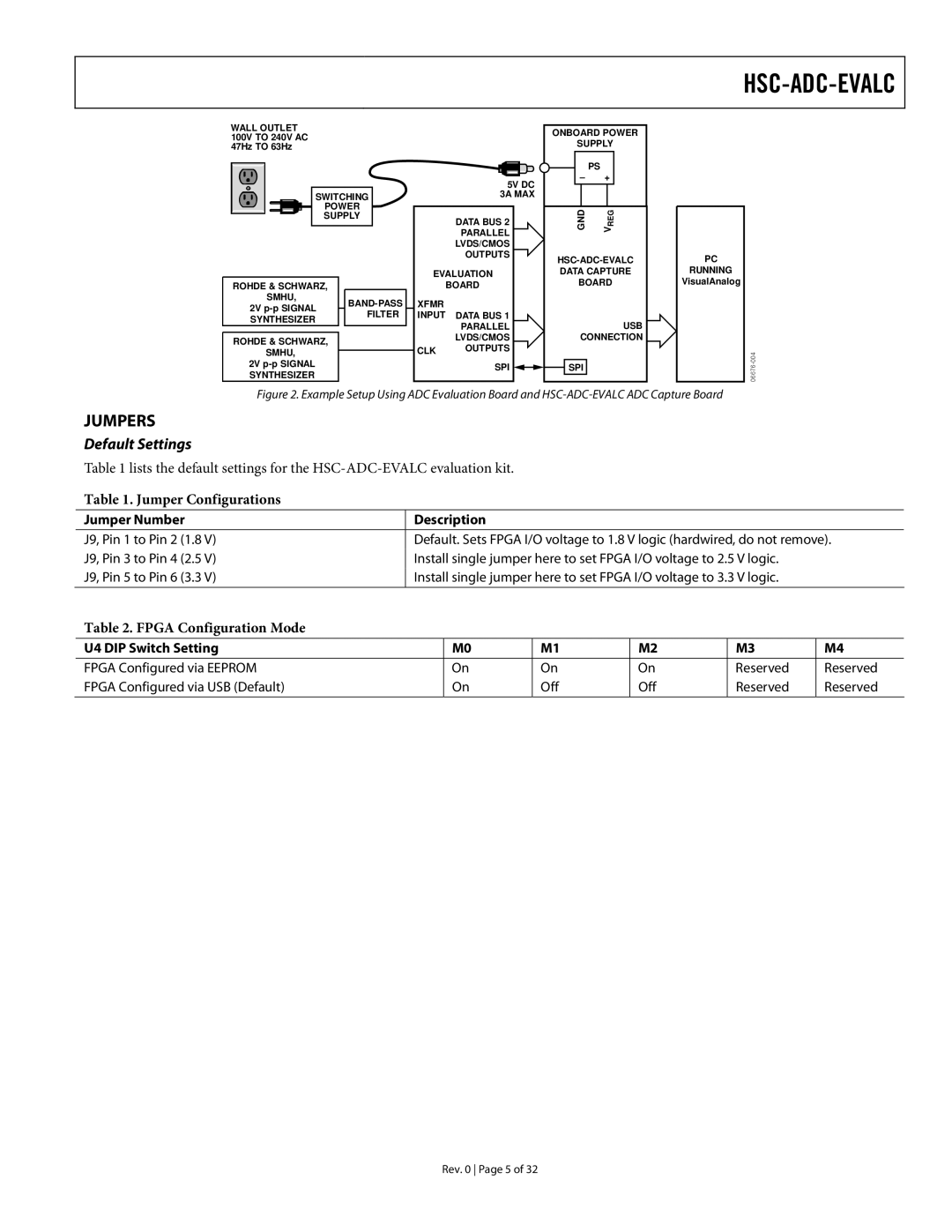

Figure 2. Example Setup Using ADC Evaluation Board and HSC-ADC-EVALC ADC Capture Board

JUMPERS

Default Settings

Table 1 lists the default settings for the

Table 1. Jumper Configurations

Jumper Number | Description |

|

|

J9, Pin 1 to Pin 2 (1.8 V) | Default. Sets FPGA I/O voltage to 1.8 V logic (hardwired, do not remove). |

J9, Pin 3 to Pin 4 (2.5 V) | Install single jumper here to set FPGA I/O voltage to 2.5 V logic. |

J9, Pin 5 to Pin 6 (3.3 V) | Install single jumper here to set FPGA I/O voltage to 3.3 V logic. |

Table 2. FPGA Configuration Mode

U4 DIP Switch Setting | M0 | M1 |

|

|

|

FPGA Configured via EEPROM | On | On |

FPGA Configured via USB (Default) | On | Off |

|

|

|

M2

On Off

M3 | M4 |

|

|

Reserved | Reserved |

Reserved | Reserved |

|

|

Rev. 0 Page 5 of 32