PRELIMINARY

CY14B104LA, CY14B104NA

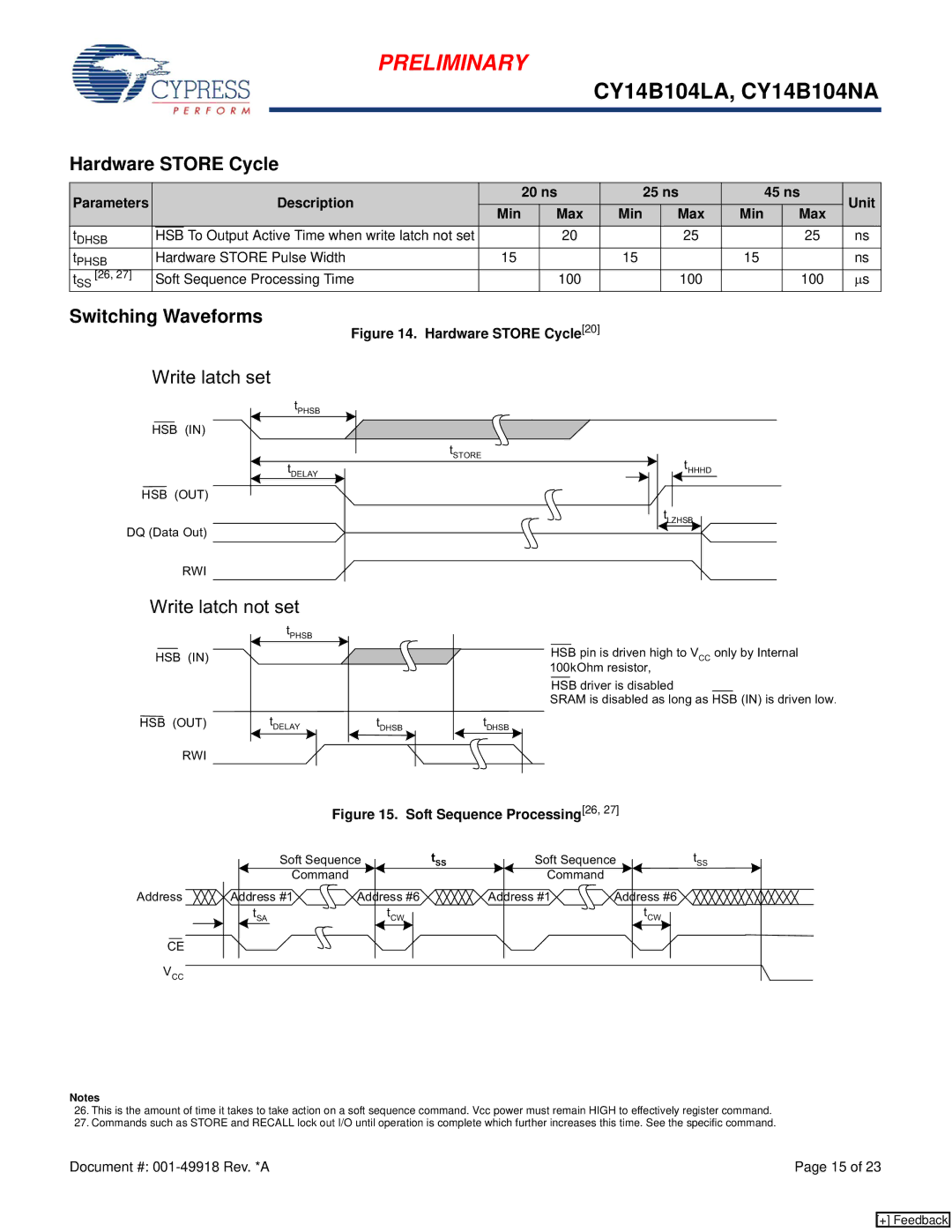

Hardware STORE Cycle

Parameters |

|

| Description |

| 20 ns |

| 25 ns |

| 45 ns | Unit | |||

|

| Min |

| Max | Min |

| Max | Min |

| Max | |||

|

|

|

|

|

|

|

| ||||||

tDHSB |

| HSB | To Output Active Time when write latch not set |

|

| 20 |

|

| 25 |

|

| 25 | ns |

tPHSB |

| Hardware STORE Pulse Width | 15 |

|

| 15 |

|

| 15 |

|

| ns | |

tSS [26, 27] |

| Soft Sequence Processing Time |

|

| 100 |

|

| 100 |

|

| 100 | μs | |

Switching Waveforms

Figure 14. Hardware STORE Cycle[20]

Write latch set

HSB (IN)

HSB (OUT)

DQ (Data Out)

RWI

tPHSB

tDELAY

tSTORE

tHHHD

tLZHSB

Write latch not set

tPHSB

HSB (IN)

HSB (OUT) | tDELAY |

tDHSB

HSB pin is driven high to VCC only by Internal 100kOhm resistor,

HSB driver is disabled

SRAM is disabled as long as HSB (IN) is driven low.

tDHSB

RWI ![]()

Figure 15. Soft Sequence Processing[26, 27]

| Soft Sequence | tSS | Soft Sequence | tSS | ||

| Command |

|

| Command |

|

|

Address | Address #1 | Address #6 | Address #1 | Address #6 |

| |

| tSA |

| tCW |

| tCW |

|

CE |

|

|

|

|

|

|

VCC |

|

|

|

|

|

|

Notes

26.This is the amount of time it takes to take action on a soft sequence command. Vcc power must remain HIGH to effectively register command.

27.Commands such as STORE and RECALL lock out I/O until operation is complete which further increases this time. See the specific command.

Document #: | Page 15 of 23 |

[+] Feedback