PRELIMINARY | CY14B104K, CY14B104M |

|

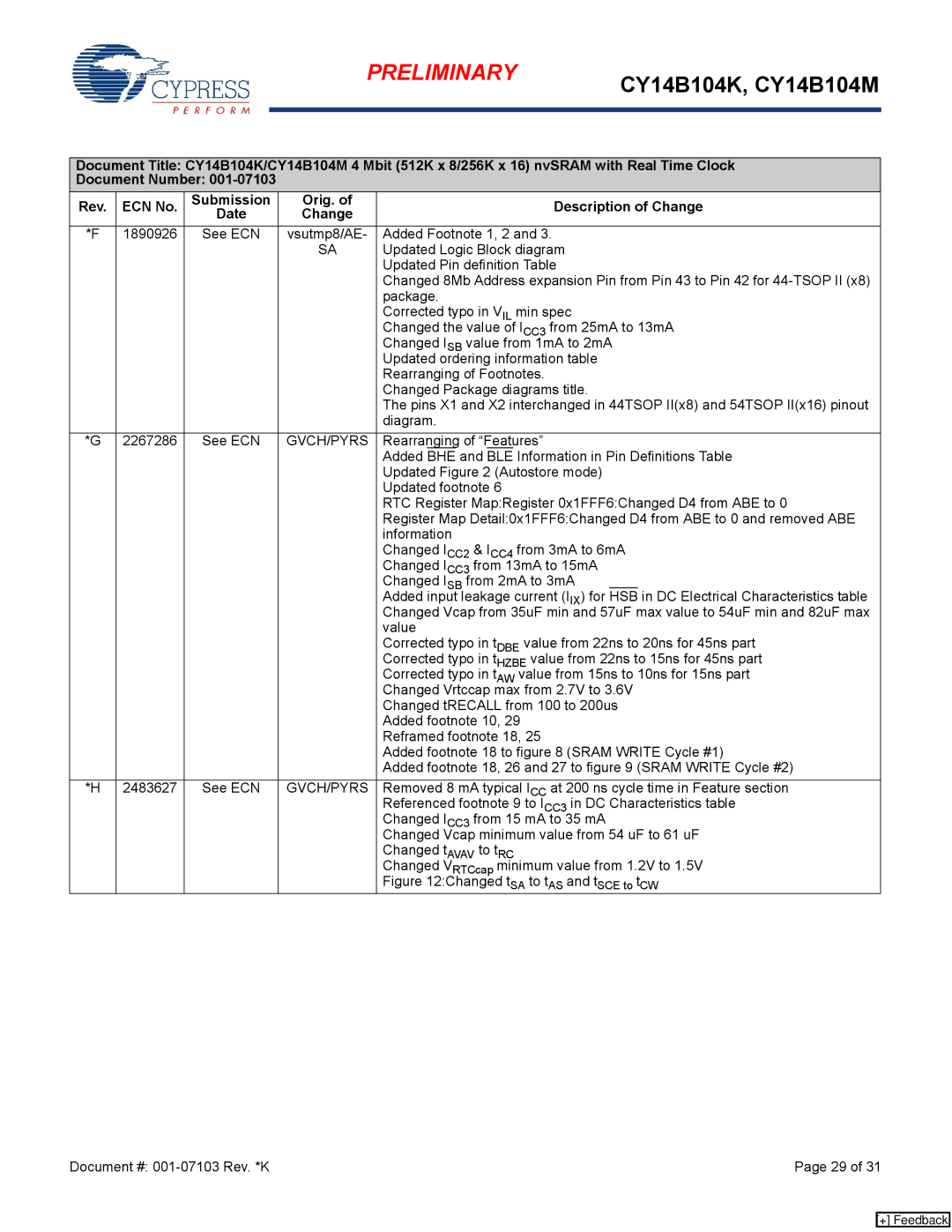

Document Title: CY14B104K/CY14B104M 4 Mbit (512K x 8/256K x 16) nvSRAM with Real Time Clock

Document Number:

Rev. | ECN No. | Submission | Orig. of | Description of Change | ||

|

| Date | Change |

|

|

|

*F | 1890926 | See ECN | vsutmp8/AE- | Added Footnote 1, 2 and 3. | ||

|

|

| SA | Updated Logic Block diagram | ||

|

|

|

| Updated Pin definition Table | ||

|

|

|

| Changed 8Mb Address expansion Pin from Pin 43 to Pin 42 for | ||

|

|

|

| package. | ||

|

|

|

| Corrected typo in VIL min spec | ||

|

|

|

| Changed the value of ICC3 from 25mA to 13mA | ||

|

|

|

| Changed ISB value from 1mA to 2mA | ||

|

|

|

| Updated ordering information table | ||

|

|

|

| Rearranging of Footnotes. | ||

|

|

|

| Changed Package diagrams title. | ||

|

|

|

| The pins X1 and X2 interchanged in 44TSOP II(x8) and 54TSOP II(x16) pinout | ||

|

|

|

| diagram. | ||

*G | 2267286 | See ECN | GVCH/PYRS | Rearranging of “Features” | ||

|

|

|

| Added BHE and BLE Information in Pin Definitions Table | ||

|

|

|

| Updated Figure 2 (Autostore mode) | ||

|

|

|

| Updated footnote 6 | ||

|

|

|

| RTC Register Map:Register 0x1FFF6:Changed D4 from ABE to 0 | ||

|

|

|

| Register Map Detail:0x1FFF6:Changed D4 from ABE to 0 and removed ABE | ||

|

|

|

| information | ||

|

|

|

| Changed ICC2 & ICC4 from 3mA to 6mA | ||

|

|

|

| Changed ICC3 from 13mA to 15mA | ||

|

|

|

| Changed ISB from 2mA to 3mA |

|

|

|

|

|

| Added input leakage current (IIX) for HSB in DC Electrical Characteristics table | ||

|

|

|

| Changed Vcap from 35uF min and 57uF max value to 54uF min and 82uF max | ||

|

|

|

| value | ||

|

|

|

| Corrected typo in tDBE value from 22ns to 20ns for 45ns part | ||

|

|

|

| Corrected typo in tHZBE value from 22ns to 15ns for 45ns part | ||

|

|

|

| Corrected typo in tAW value from 15ns to 10ns for 15ns part | ||

|

|

|

| Changed Vrtccap max from 2.7V to 3.6V | ||

|

|

|

| Changed tRECALL from 100 to 200us | ||

|

|

|

| Added footnote 10, 29 | ||

|

|

|

| Reframed footnote 18, 25 | ||

|

|

|

| Added footnote 18 to figure 8 (SRAM WRITE Cycle #1) | ||

|

|

|

| Added footnote 18, 26 and 27 to figure 9 (SRAM WRITE Cycle #2) | ||

*H | 2483627 | See ECN | GVCH/PYRS | Removed 8 mA typical ICC at 200 ns cycle time in Feature section | ||

|

|

|

| Referenced footnote 9 to ICC3 in DC Characteristics table | ||

|

|

|

| Changed ICC3 from 15 mA to 35 mA | ||

|

|

|

| Changed Vcap minimum value from 54 uF to 61 uF | ||

|

|

|

| Changed tAVAV to tRC | ||

|

|

|

| Changed VRTCcap minimum value from 1.2V to 1.5V | ||

|

|

|

| Figure 12:Changed tSA to tAS and tSCE to tCW | ||

Document #: | Page 29 of 31 |

[+] Feedback