PRELIMINARY | CY14B104K, CY14B104M |

|

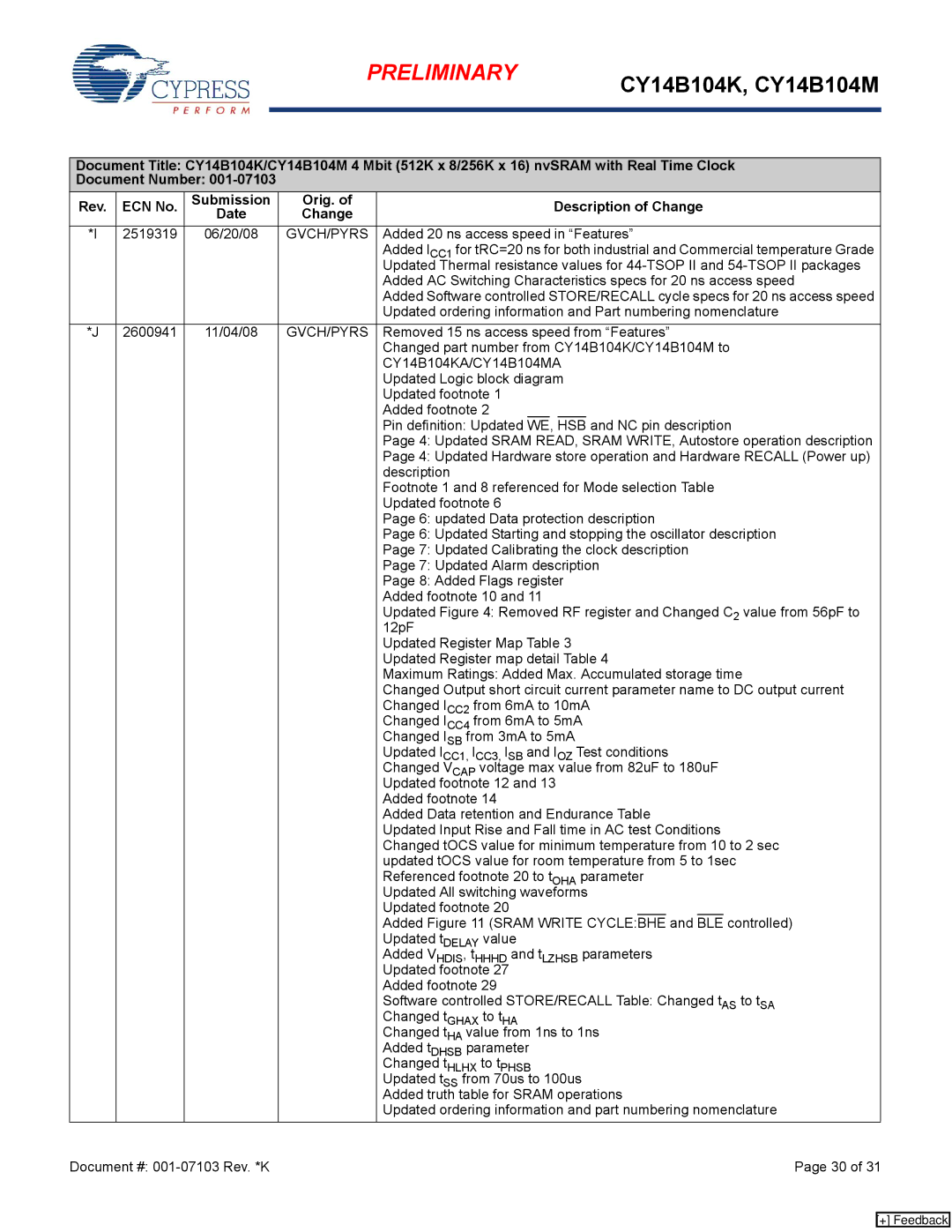

Document Title: CY14B104K/CY14B104M 4 Mbit (512K x 8/256K x 16) nvSRAM with Real Time Clock

Document Number:

Rev. | ECN No. | Submission | Orig. of |

|

| Description of Change |

| ||||||

|

| Date | Change |

|

|

|

|

|

|

|

|

|

|

*I | 2519319 | 06/20/08 | GVCH/PYRS | Added 20 ns access speed in “Features” |

| ||||||||

|

|

|

| Added ICC1 for tRC=20 ns for both industrial and Commercial temperature Grade | |||||||||

|

|

|

| Updated Thermal resistance values for | |||||||||

|

|

|

| Added AC Switching Characteristics specs for 20 ns access speed | |||||||||

|

|

|

| Added Software controlled STORE/RECALL cycle specs for 20 ns access speed | |||||||||

|

|

|

| Updated ordering information and Part numbering nomenclature | |||||||||

*J | 2600941 | 11/04/08 | GVCH/PYRS | Removed 15 ns access speed from “Features” |

| ||||||||

|

|

|

| Changed part number from CY14B104K/CY14B104M to | |||||||||

|

|

|

| CY14B104KA/CY14B104MA | |||||||||

|

|

|

| Updated Logic block diagram | |||||||||

|

|

|

| Updated footnote 1 | |||||||||

|

|

|

| Added footnote 2 | |||||||||

|

|

|

| Pin definition: Updated | WE, |

| HSB | and NC pin description | |||||

|

|

|

| Page 4: Updated SRAM READ, SRAM WRITE, Autostore operation description | |||||||||

|

|

|

| Page 4: Updated Hardware store operation and Hardware RECALL (Power up) | |||||||||

|

|

|

| description | |||||||||

|

|

|

| Footnote 1 and 8 referenced for Mode selection Table | |||||||||

|

|

|

| Updated footnote 6 | |||||||||

|

|

|

| Page 6: updated Data protection description | |||||||||

|

|

|

| Page 6: Updated Starting and stopping the oscillator description | |||||||||

|

|

|

| Page 7: Updated Calibrating the clock description | |||||||||

|

|

|

| Page 7: Updated Alarm description | |||||||||

|

|

|

| Page 8: Added Flags register | |||||||||

|

|

|

| Added footnote 10 and 11 | |||||||||

|

|

|

| Updated Figure 4: Removed RF register and Changed C2 value from 56pF to | |||||||||

|

|

|

| 12pF | |||||||||

|

|

|

| Updated Register Map Table 3 | |||||||||

|

|

|

| Updated Register map detail Table 4 | |||||||||

|

|

|

| Maximum Ratings: Added Max. Accumulated storage time | |||||||||

|

|

|

| Changed Output short circuit current parameter name to DC output current | |||||||||

|

|

|

| Changed ICC2 from 6mA to 10mA | |||||||||

|

|

|

| Changed ICC4 from 6mA to 5mA | |||||||||

|

|

|

| Changed ISB from 3mA to 5mA | |||||||||

|

|

|

| Updated ICC1, ICC3, ISB and IOZ Test conditions | |||||||||

|

|

|

| Changed VCAP voltage max value from 82uF to 180uF | |||||||||

|

|

|

| Updated footnote 12 and 13 | |||||||||

|

|

|

| Added footnote 14 | |||||||||

|

|

|

| Added Data retention and Endurance Table | |||||||||

|

|

|

| Updated Input Rise and Fall time in AC test Conditions | |||||||||

|

|

|

| Changed tOCS value for minimum temperature from 10 to 2 sec | |||||||||

|

|

|

| updated tOCS value for room temperature from 5 to 1sec | |||||||||

|

|

|

| Referenced footnote 20 to tOHA parameter | |||||||||

|

|

|

| Updated All switching waveforms | |||||||||

|

|

|

| Updated footnote 20 |

|

|

|

| |||||

|

|

|

| Added Figure 11 (SRAM WRITE CYCLE:BHE | and BLE controlled) | ||||||||

|

|

|

| Updated tDELAY value | |||||||||

|

|

|

| Added VHDIS, tHHHD and tLZHSB parameters | |||||||||

|

|

|

| Updated footnote 27 | |||||||||

|

|

|

| Added footnote 29 | |||||||||

|

|

|

| Software controlled STORE/RECALL Table: Changed tAS to tSA | |||||||||

|

|

|

| Changed tGHAX to tHA | |||||||||

|

|

|

| Changed tHA value from 1ns to 1ns | |||||||||

|

|

|

| Added tDHSB parameter | |||||||||

|

|

|

| Changed tHLHX to tPHSB | |||||||||

|

|

|

| Updated tSS from 70us to 100us | |||||||||

|

|

|

| Added truth table for SRAM operations | |||||||||

|

|

|

| Updated ordering information and part numbering nomenclature | |||||||||

Document #: |

|

|

|

|

|

|

|

|

| Page 30 of 31 | |||

[+] Feedback