CY7C1471V25

CY7C1473V25

CY7C1475V25

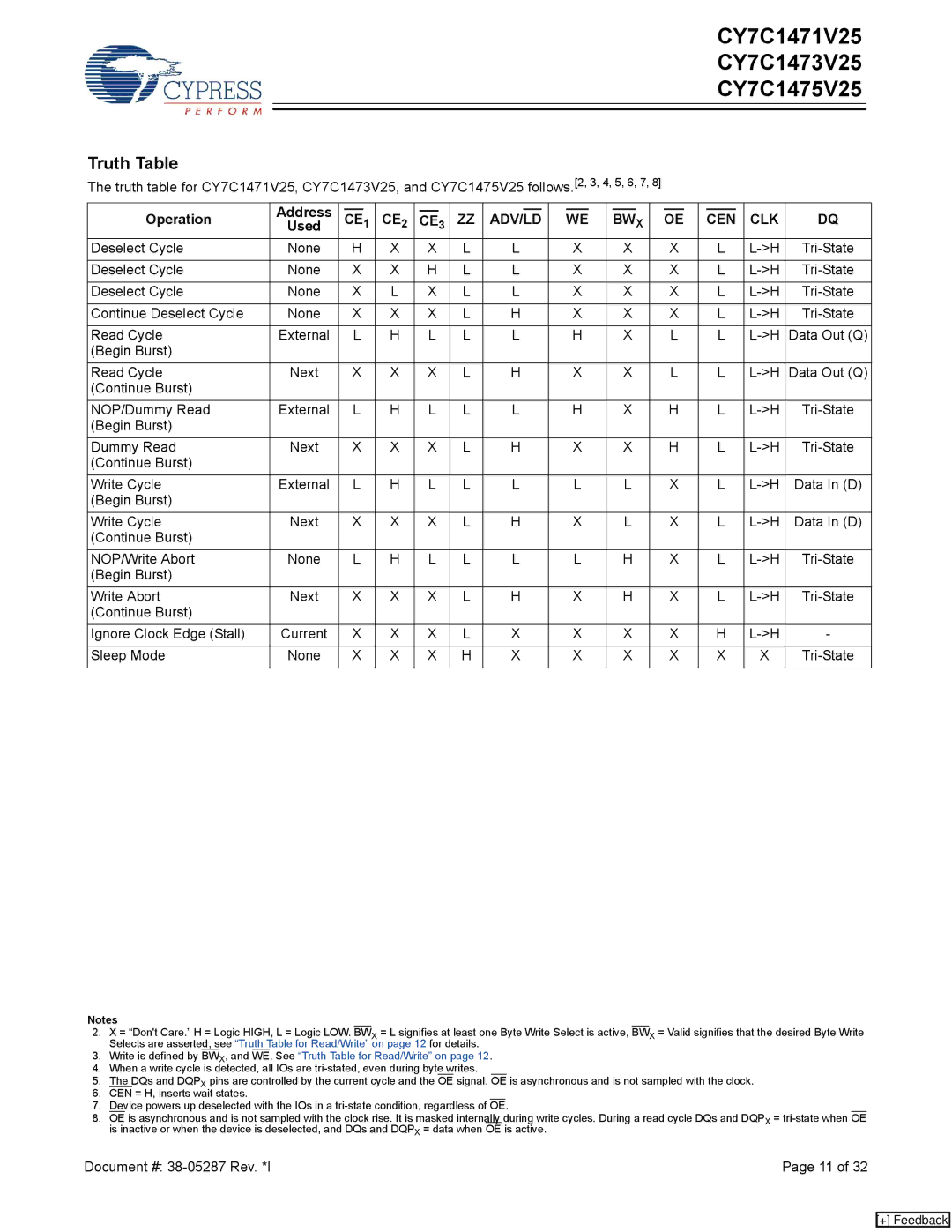

Truth Table

The truth table for CY7C1471V25, CY7C1473V25, and CY7C1475V25 follows.[2, 3, 4, 5, 6, 7, 8]

| Address |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Operation | CE1 | CE2 | CE3 | ZZ | ADV/LD |

| WE |

|

| BWX |

| OE |

|

| CEN | CLK | DQ | |||||||||

Used |

|

|

|

|

|

|

| |||||||||||||||||||

Deselect Cycle | None |

| H | X |

| X |

| L | L |

| X |

|

| X |

| X |

|

| L | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

Deselect Cycle | None |

| X | X |

| H |

| L | L |

| X |

|

| X |

| X |

|

| L | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

Deselect Cycle | None |

| X | L |

| X |

| L | L |

| X |

|

| X |

| X |

|

| L | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

Continue Deselect Cycle | None |

| X | X |

| X |

| L | H |

| X |

|

| X |

| X |

|

| L | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

Read Cycle | External |

| L | H |

| L |

| L | L |

| H |

|

| X |

| L |

|

| L | Data Out (Q) | ||||||

(Begin Burst) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Read Cycle | Next |

| X | X |

| X |

| L | H |

| X |

|

| X |

| L |

|

| L | Data Out (Q) | ||||||

(Continue Burst) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOP/Dummy Read | External |

| L | H |

| L |

| L | L |

| H |

|

| X |

| H |

|

| L | |||||||

(Begin Burst) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Dummy Read | Next |

| X | X |

| X |

| L | H |

| X |

|

| X |

| H |

|

| L | |||||||

(Continue Burst) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write Cycle | External |

| L | H |

| L |

| L | L |

| L |

|

| L |

| X |

|

| L | Data In (D) | ||||||

(Begin Burst) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write Cycle | Next |

| X | X |

| X |

| L | H |

| X |

|

| L |

| X |

|

| L | Data In (D) | ||||||

(Continue Burst) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOP/Write Abort | None |

| L | H |

| L |

| L | L |

| L |

|

| H |

| X |

|

| L | |||||||

(Begin Burst) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write Abort | Next |

| X | X |

| X |

| L | H |

| X |

|

| H |

| X |

|

| L | |||||||

(Continue Burst) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ignore Clock Edge (Stall) | Current |

| X | X |

| X |

| L | X |

| X |

|

| X |

| X |

|

| H | - | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

Sleep Mode | None |

| X | X |

| X |

| H | X |

| X |

|

| X |

| X |

|

| X | X | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Notes

2.X = “Don't Care.” H = Logic HIGH, L = Logic LOW. BWX = L signifies at least one Byte Write Select is active, BWX = Valid signifies that the desired Byte Write Selects are asserted, see “Truth Table for Read/Write” on page 12 for details.

3.Write is defined by BWX, and WE. See “Truth Table for Read/Write” on page 12.

4.When a write cycle is detected, all IOs are

5.The DQs and DQPX pins are controlled by the current cycle and the OE signal. OE is asynchronous and is not sampled with the clock.

6.CEN = H, inserts wait states.

7.Device powers up deselected with the IOs in a

8.OE is asynchronous and is not sampled with the clock rise. It is masked internally during write cycles. During a read cycle DQs and DQPX =

Document #: | Page 11 of 32 |

[+] Feedback