CYV15G0104TRB

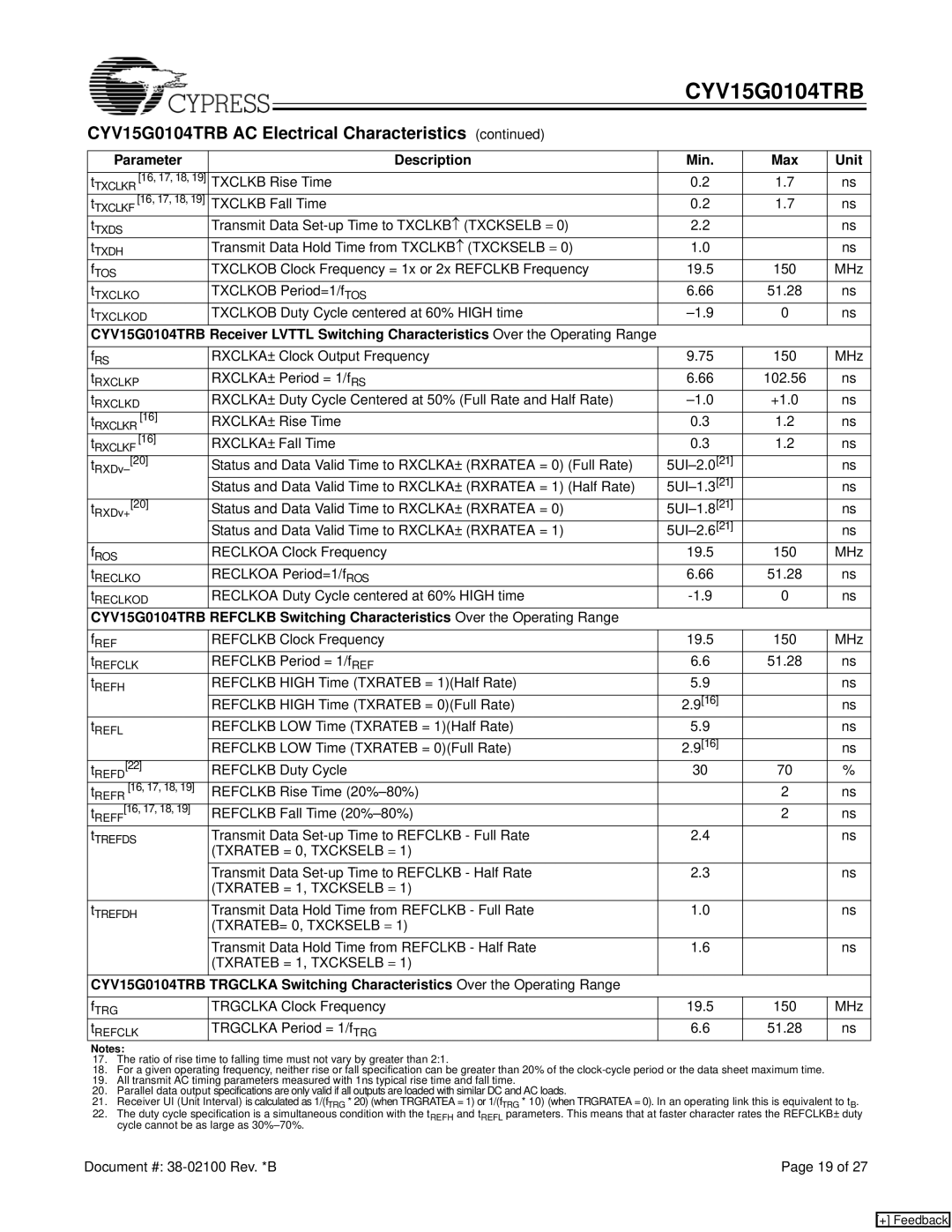

CYV15G0104TRB AC Electrical Characteristics (continued)

Parameter | Description | Min. | Max | Unit | |

t | [16, 17, 18, 19] | TXCLKB Rise Time | 0.2 | 1.7 | ns |

TXCLKR |

|

|

|

| |

t | [16, 17, 18, 19] | TXCLKB Fall Time | 0.2 | 1.7 | ns |

TXCLKF |

|

|

|

| |

tTXDS |

| Transmit Data | 2.2 |

| ns |

tTXDH |

| Transmit Data Hold Time from TXCLKB↑ (TXCKSELB = 0) | 1.0 |

| ns |

fTOS |

| TXCLKOB Clock Frequency = 1x or 2x REFCLKB Frequency | 19.5 | 150 | MHz |

tTXCLKO | TXCLKOB Period=1/fTOS | 6.66 | 51.28 | ns | |

tTXCLKOD | TXCLKOB Duty Cycle centered at 60% HIGH time | 0 | ns | ||

CYV15G0104TRB Receiver LVTTL Switching Characteristics Over the Operating Range |

|

|

| ||

fRS |

| RXCLKA± Clock Output Frequency | 9.75 | 150 | MHz |

tRXCLKP | RXCLKA± Period = 1/fRS | 6.66 | 102.56 | ns | |

tRXCLKD | RXCLKA± Duty Cycle Centered at 50% (Full Rate and Half Rate) | +1.0 | ns | ||

tRXCLKR [16] | RXCLKA± Rise Time | 0.3 | 1.2 | ns | |

tRXCLKF [16] | RXCLKA± Fall Time | 0.3 | 1.2 | ns | |

t | [20] | Status and Data Valid Time to RXCLKA± (RXRATEA = 0) (Full Rate) |

| ns | |

RXDv– |

|

|

|

| |

|

| Status and Data Valid Time to RXCLKA± (RXRATEA = 1) (Half Rate) |

| ns | |

t | [20] | Status and Data Valid Time to RXCLKA± (RXRATEA = 0) |

| ns | |

RXDv+ |

|

|

| ||

|

| Status and Data Valid Time to RXCLKA± (RXRATEA = 1) |

| ns | |

fROS |

| RECLKOA Clock Frequency | 19.5 | 150 | MHz |

tRECLKO | RECLKOA Period=1/fROS | 6.66 | 51.28 | ns | |

tRECLKOD | RECLKOA Duty Cycle centered at 60% HIGH time | 0 | ns | ||

CYV15G0104TRB REFCLKB Switching Characteristics Over the Operating Range |

|

|

| ||

fREF |

| REFCLKB Clock Frequency | 19.5 | 150 | MHz |

tREFCLK | REFCLKB Period = 1/fREF | 6.6 | 51.28 | ns | |

tREFH |

| REFCLKB HIGH Time (TXRATEB = 1)(Half Rate) | 5.9 |

| ns |

|

| REFCLKB HIGH Time (TXRATEB = 0)(Full Rate) | 2.9[16] |

| ns |

tREFL |

| REFCLKB LOW Time (TXRATEB = 1)(Half Rate) | 5.9 |

| ns |

|

| REFCLKB LOW Time (TXRATEB = 0)(Full Rate) | 2.9[16] |

| ns |

tREFD[22] | REFCLKB Duty Cycle | 30 | 70 | % | |

tREFR [16, 17, 18, 19] | REFCLKB Rise Time |

| 2 | ns | |

tREFF[16, 17, 18, 19] | REFCLKB Fall Time |

| 2 | ns | |

tTREFDS | Transmit Data | 2.4 |

| ns | |

|

| (TXRATEB = 0, TXCKSELB = 1) |

|

|

|

|

| Transmit Data | 2.3 |

| ns |

|

| (TXRATEB = 1, TXCKSELB = 1) |

|

|

|

tTREFDH | Transmit Data Hold Time from REFCLKB - Full Rate | 1.0 |

| ns | |

|

| (TXRATEB= 0, TXCKSELB = 1) |

|

|

|

|

| Transmit Data Hold Time from REFCLKB - Half Rate | 1.6 |

| ns |

|

| (TXRATEB = 1, TXCKSELB = 1) |

|

|

|

CYV15G0104TRB TRGCLKA Switching Characteristics Over the Operating Range |

|

|

| ||

fTRG |

| TRGCLKA Clock Frequency | 19.5 | 150 | MHz |

tREFCLK | TRGCLKA Period = 1/fTRG | 6.6 | 51.28 | ns | |

Notes:

17.The ratio of rise time to falling time must not vary by greater than 2:1.

18.For a given operating frequency, neither rise or fall specification can be greater than 20% of the

19.All transmit AC timing parameters measured with 1ns typical rise time and fall time.

20.Parallel data output specifications are only valid if all outputs are loaded with similar DC and AC loads.

21.Receiver UI (Unit Interval) is calculated as 1/(fTRG * 20) (when TRGRATEA = 1) or 1/(fTRG * 10) (when TRGRATEA = 0). In an operating link this is equivalent to tB.

22.The duty cycle specification is a simultaneous condition with the tREFH and tREFL parameters. This means that at faster character rates the REFCLKB± duty cycle cannot be as large as

Document #: | Page 19 of 27 |

[+] Feedback