CYV15G0104TRB

Pin Definitions (continued)

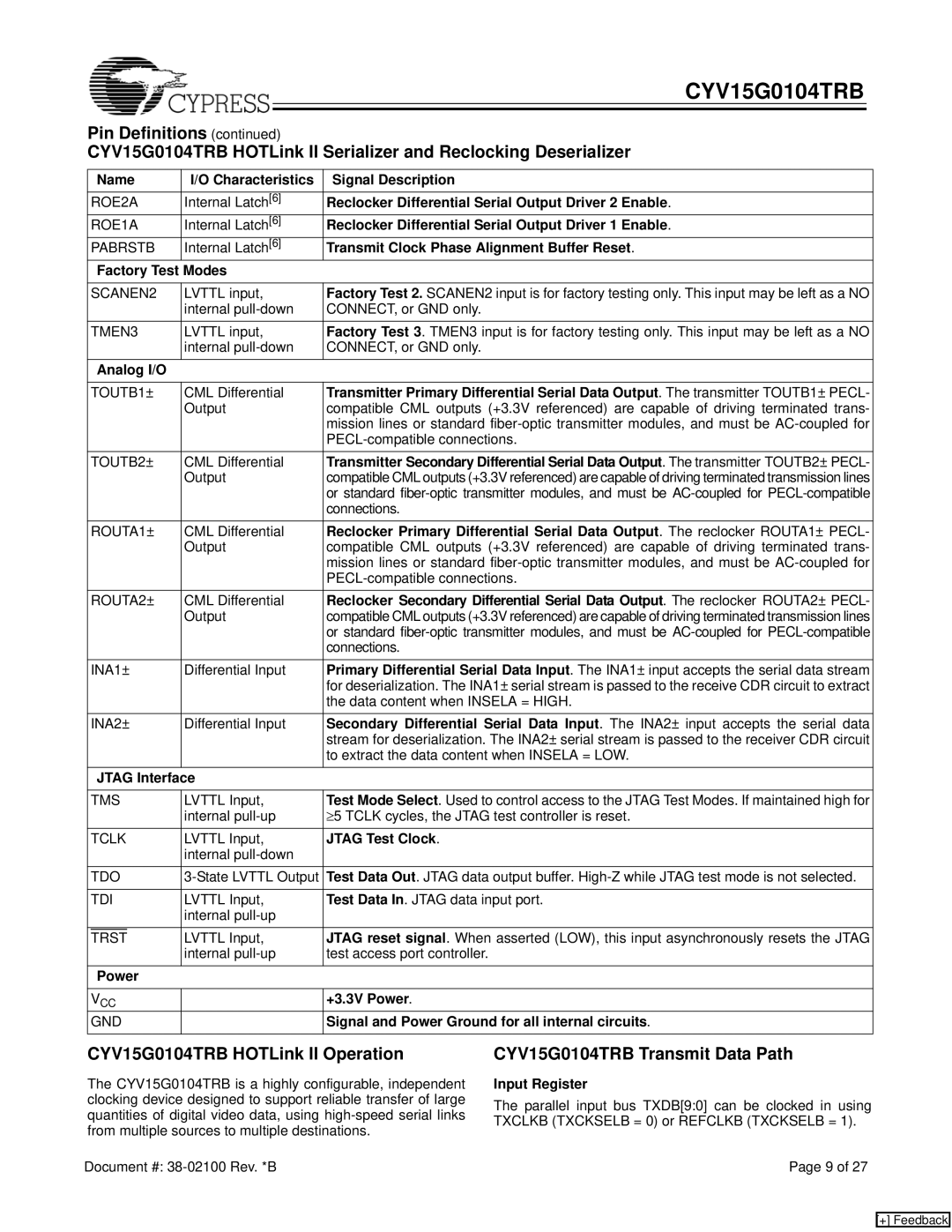

CYV15G0104TRB HOTLink II Serializer and Reclocking Deserializer

Name | I/O Characteristics | Signal Description |

ROE2A | Internal Latch[6] | Reclocker Differential Serial Output Driver 2 Enable. |

ROE1A | Internal Latch[6] | Reclocker Differential Serial Output Driver 1 Enable. |

PABRSTB | Internal Latch[6] | Transmit Clock Phase Alignment Buffer Reset. |

Factory Test Modes |

| |

SCANEN2 | LVTTL input, | Factory Test 2. SCANEN2 input is for factory testing only. This input may be left as a NO |

| internal | CONNECT, or GND only. |

TMEN3 | LVTTL input, | Factory Test 3. TMEN3 input is for factory testing only. This input may be left as a NO |

| internal | CONNECT, or GND only. |

Analog I/O |

|

|

TOUTB1± | CML Differential | Transmitter Primary Differential Serial Data Output. The transmitter TOUTB1± PECL- |

| Output | compatible CML outputs (+3.3V referenced) are capable of driving terminated trans- |

|

| mission lines or standard |

|

| |

TOUTB2± | CML Differential | Transmitter Secondary Differential Serial Data Output. The transmitter TOUTB2± PECL- |

| Output | compatible CML outputs (+3.3V referenced) are capable of driving terminated transmission lines |

|

| or standard |

|

| connections. |

ROUTA1± | CML Differential | Reclocker Primary Differential Serial Data Output. The reclocker ROUTA1± PECL- |

| Output | compatible CML outputs (+3.3V referenced) are capable of driving terminated trans- |

|

| mission lines or standard |

|

| |

ROUTA2± | CML Differential | Reclocker Secondary Differential Serial Data Output. The reclocker ROUTA2± PECL- |

| Output | compatible CML outputs (+3.3V referenced) are capable of driving terminated transmission lines |

|

| or standard |

|

| connections. |

INA1± | Differential Input | Primary Differential Serial Data Input. The INA1± input accepts the serial data stream |

|

| for deserialization. The INA1± serial stream is passed to the receive CDR circuit to extract |

|

| the data content when INSELA = HIGH. |

INA2± | Differential Input | Secondary Differential Serial Data Input. The INA2± input accepts the serial data |

|

| stream for deserialization. The INA2± serial stream is passed to the receiver CDR circuit |

|

| to extract the data content when INSELA = LOW. |

JTAG Interface |

| |

TMS | LVTTL Input, | Test Mode Select. Used to control access to the JTAG Test Modes. If maintained high for |

| internal | ≥5 TCLK cycles, the JTAG test controller is reset. |

TCLK | LVTTL Input, | JTAG Test Clock. |

| internal |

|

TDO | Test Data Out. JTAG data output buffer. | |

TDI | LVTTL Input, | Test Data In. JTAG data input port. |

| internal |

|

TRST | LVTTL Input, | JTAG reset signal. When asserted (LOW), this input asynchronously resets the JTAG |

| internal | test access port controller. |

Power |

|

|

VCC |

| +3.3V Power. |

GND |

| Signal and Power Ground for all internal circuits. |

CYV15G0104TRB HOTLink II Operation

The CYV15G0104TRB is a highly configurable, independent clocking device designed to support reliable transfer of large quantities of digital video data, using

Document #:

CYV15G0104TRB Transmit Data Path

Input Register

The parallel input bus TXDB[9:0] can be clocked in using TXCLKB (TXCKSELB = 0) or REFCLKB (TXCKSELB = 1).

Page 9 of 27

[+] Feedback