CYV15G0404RB

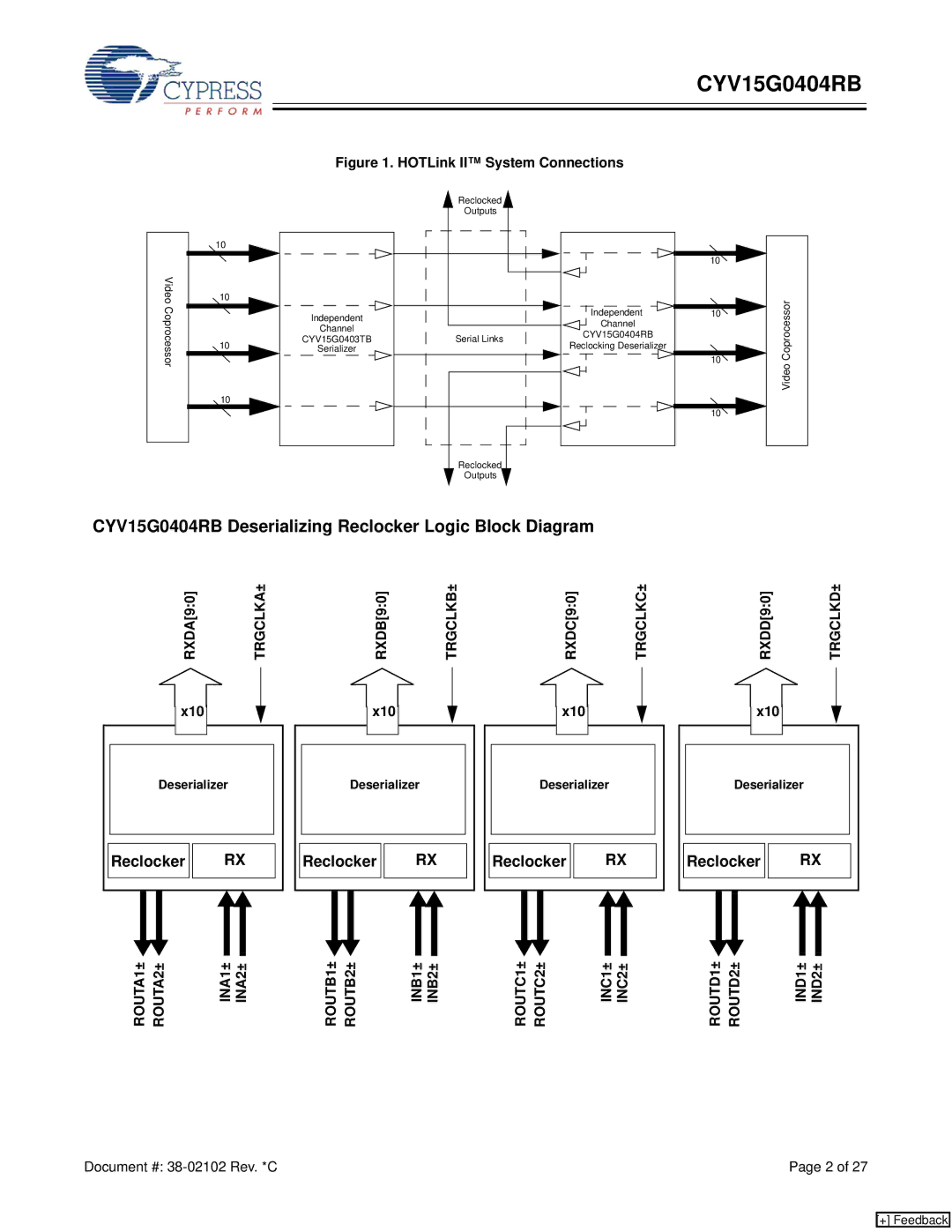

Figure 1. HOTLink II™ System Connections

Video Coprocessor

10

10

10

10

Independent

Channel

CYV15G0403TB

Serializer

Reclocked

Outputs

Serial Links

Reclocked

Outputs ![]()

Independent

Channel

CYV15G0404RB

Reclocking Deserializer

10

10

10

10

Video Coprocessor

CYV15G0404RB Deserializing Reclocker Logic Block Diagram

| RXDA[9:0] |

| TRGCLKA± | |

| x10 |

|

|

|

|

|

|

| |

|

|

|

| |

|

|

|

| |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RXDB[9:0] |

| TRGCLKB± | |

| x10 |

|

|

|

|

|

|

| |

|

|

|

| |

|

|

|

| |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RXDC[9:0] |

| TRGCLKC± | |

| x10 |

|

|

|

|

|

|

| |

|

|

|

| |

|

|

|

| |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RXDD[9:0] |

| TRGCLKD± | |

| x10 |

|

|

|

|

|

|

| |

|

|

|

| |

|

|

|

| |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Deserializer

Reclocker ![]()

![]() RX

RX

Deserializer

Reclocker ![]()

![]() RX

RX

Deserializer

Reclocker ![]()

![]() RX

RX

Deserializer

Reclocker ![]()

![]() RX

RX

ROUTA1± ROUTA2± | INA1± INA2± | ROUTB1± ROUTB2± | INB1± INB2± | ROUTC1± ROUTC2± | INC1± INC2± | ROUTD1± ROUTD2± | IND1± IND2± |

Document #: | Page 2 of 27 |

[+] Feedback