CYV15G0404RB

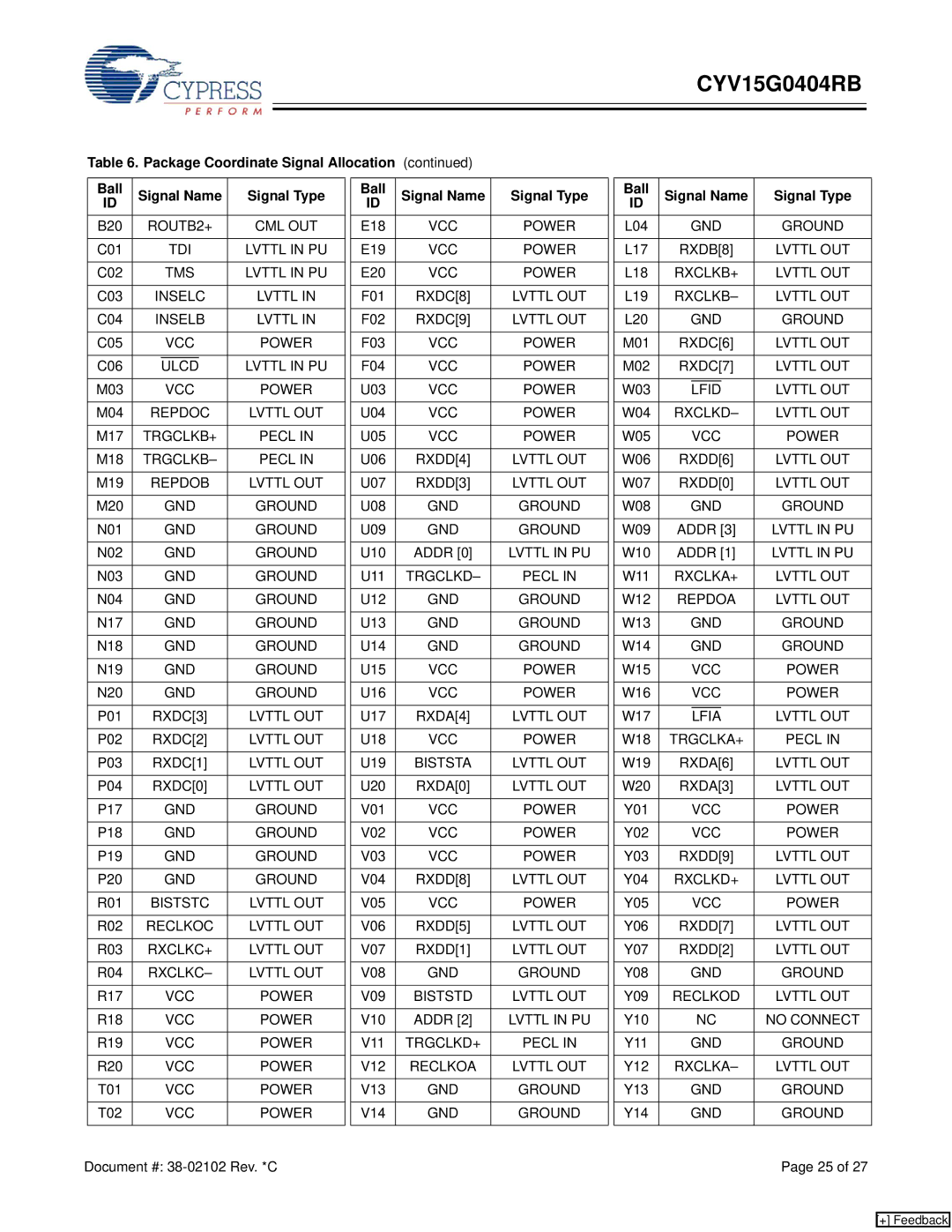

| Table 6. Package Coordinate Signal Allocation (continued) |

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

| Ball | Signal Name | Signal Type |

| Ball | Signal Name | Signal Type |

| Ball | Signal Name | Signal Type | |||||

| ID |

|

|

|

|

| ID |

|

|

| ID |

|

|

|

|

|

| B20 | ROUTB2+ | CML OUT |

| E18 | VCC | POWER |

| L04 | GND | GROUND | |||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| C01 |

| TDI | LVTTL IN PU |

| E19 | VCC | POWER |

| L17 | RXDB[8] | LVTTL OUT | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| C02 |

| TMS | LVTTL IN PU |

| E20 | VCC | POWER |

| L18 | RXCLKB+ | LVTTL OUT | ||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

| C03 | INSELC | LVTTL IN |

| F01 | RXDC[8] | LVTTL OUT |

| L19 | RXCLKB– | LVTTL OUT | |||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

| C04 | INSELB | LVTTL IN |

| F02 | RXDC[9] | LVTTL OUT |

| L20 | GND | GROUND | |||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| C05 |

| VCC | POWER |

| F03 | VCC | POWER |

| M01 | RXDC[6] | LVTTL OUT | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| C06 |

|

|

| LVTTL IN PU |

| F04 | VCC | POWER |

| M02 | RXDC[7] | LVTTL OUT | |||

ULCD | ||||||||||||||||

| M03 |

| VCC | POWER |

| U03 | VCC | POWER |

| W03 |

|

|

|

| LVTTL OUT | |

| LFID | |||||||||||||||

| M04 | REPDOC | LVTTL OUT |

| U04 | VCC | POWER |

| W04 | RXCLKD– | LVTTL OUT | |||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| M17 | TRGCLKB+ | PECL IN |

| U05 | VCC | POWER |

| W05 |

| VCC | POWER | ||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

| M18 | TRGCLKB– | PECL IN |

| U06 | RXDD[4] | LVTTL OUT |

| W06 | RXDD[6] | LVTTL OUT | |||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

| M19 | REPDOB | LVTTL OUT |

| U07 | RXDD[3] | LVTTL OUT |

| W07 | RXDD[0] | LVTTL OUT | |||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| M20 |

| GND | GROUND |

| U08 | GND | GROUND |

| W08 | GND | GROUND | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| N01 |

| GND | GROUND |

| U09 | GND | GROUND |

| W09 | ADDR [3] | LVTTL IN PU | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| N02 |

| GND | GROUND |

| U10 | ADDR [0] | LVTTL IN PU |

| W10 | ADDR [1] | LVTTL IN PU | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| N03 |

| GND | GROUND |

| U11 | TRGCLKD– | PECL IN |

| W11 | RXCLKA+ | LVTTL OUT | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| N04 |

| GND | GROUND |

| U12 | GND | GROUND |

| W12 | REPDOA | LVTTL OUT | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| N17 |

| GND | GROUND |

| U13 | GND | GROUND |

| W13 | GND | GROUND | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| N18 |

| GND | GROUND |

| U14 | GND | GROUND |

| W14 | GND | GROUND | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| N19 |

| GND | GROUND |

| U15 | VCC | POWER |

| W15 |

| VCC | POWER | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| N20 |

| GND | GROUND |

| U16 | VCC | POWER |

| W16 |

| VCC | POWER | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| P01 | RXDC[3] | LVTTL OUT |

| U17 | RXDA[4] | LVTTL OUT |

| W17 |

|

|

| LVTTL OUT | |||

| LFIA | |||||||||||||||

| P02 | RXDC[2] | LVTTL OUT |

| U18 | VCC | POWER |

| W18 | TRGCLKA+ | PECL IN | |||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

| P03 | RXDC[1] | LVTTL OUT |

| U19 | BISTSTA | LVTTL OUT |

| W19 | RXDA[6] | LVTTL OUT | |||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

| P04 | RXDC[0] | LVTTL OUT |

| U20 | RXDA[0] | LVTTL OUT |

| W20 | RXDA[3] | LVTTL OUT | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| P17 |

| GND | GROUND |

| V01 | VCC | POWER |

| Y01 |

| VCC | POWER | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| P18 |

| GND | GROUND |

| V02 | VCC | POWER |

| Y02 |

| VCC | POWER | |||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| P19 |

| GND | GROUND |

| V03 | VCC | POWER |

| Y03 | RXDD[9] | LVTTL OUT | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| P20 |

| GND | GROUND |

| V04 | RXDD[8] | LVTTL OUT |

| Y04 | RXCLKD+ | LVTTL OUT | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| R01 | BISTSTC | LVTTL OUT |

| V05 | VCC | POWER |

| Y05 |

| VCC | POWER | ||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

| R02 | RECLKOC | LVTTL OUT |

| V06 | RXDD[5] | LVTTL OUT |

| Y06 | RXDD[7] | LVTTL OUT | |||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

| R03 | RXCLKC+ | LVTTL OUT |

| V07 | RXDD[1] | LVTTL OUT |

| Y07 | RXDD[2] | LVTTL OUT | |||||

|

|

|

|

|

|

|

|

|

|

|

| |||||

| R04 | RXCLKC– | LVTTL OUT |

| V08 | GND | GROUND |

| Y08 | GND | GROUND | |||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| R17 |

| VCC | POWER |

| V09 | BISTSTD | LVTTL OUT |

| Y09 | RECLKOD | LVTTL OUT | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| R18 |

| VCC | POWER |

| V10 | ADDR [2] | LVTTL IN PU |

| Y10 |

| NC | NO CONNECT | |||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| R19 |

| VCC | POWER |

| V11 | TRGCLKD+ | PECL IN |

| Y11 | GND | GROUND | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| R20 |

| VCC | POWER |

| V12 | RECLKOA | LVTTL OUT |

| Y12 | RXCLKA– | LVTTL OUT | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| T01 |

| VCC | POWER |

| V13 | GND | GROUND |

| Y13 | GND | GROUND | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| T02 |

| VCC | POWER |

| V14 | GND | GROUND |

| Y14 | GND | GROUND | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Document #: |

|

|

|

|

|

|

|

|

|

| Page 25 of 27 | |||||

[+] Feedback