CYV15G0404RB

Pin Definitions (continued)

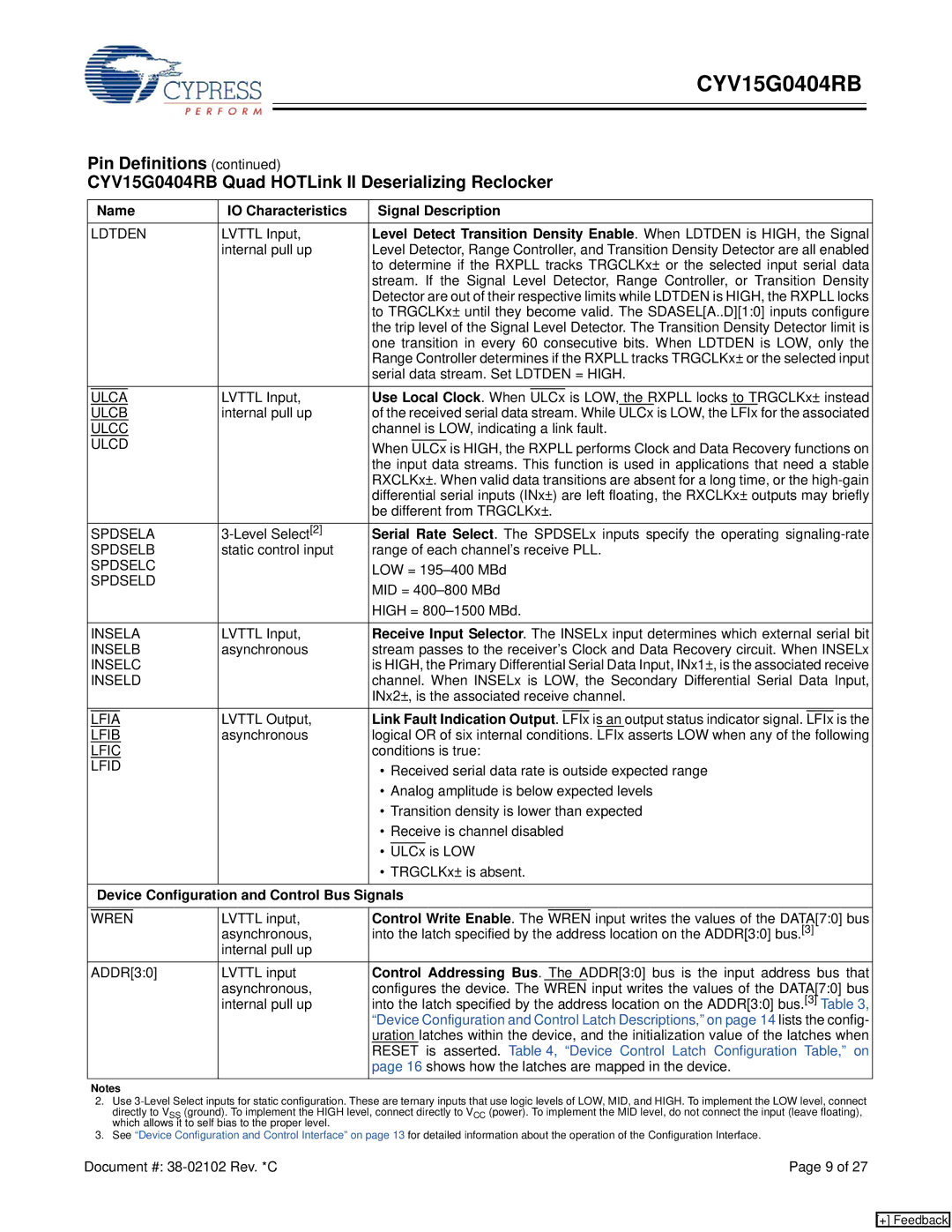

CYV15G0404RB Quad HOTLink II Deserializing Reclocker

| Name | IO Characteristics | Signal Description | |||||||||||||||||||||

|

|

|

| |||||||||||||||||||||

| LDTDEN | LVTTL Input, | Level Detect Transition Density Enable. When LDTDEN is HIGH, the Signal | |||||||||||||||||||||

|

|

|

|

| internal pull up | Level Detector, Range Controller, and Transition Density Detector are all enabled | ||||||||||||||||||

|

|

|

|

|

| to determine if the RXPLL tracks TRGCLKx± or the selected input serial data | ||||||||||||||||||

|

|

|

|

|

| stream. If the Signal Level Detector, Range Controller, or Transition Density | ||||||||||||||||||

|

|

|

|

|

| Detector are out of their respective limits while LDTDEN is HIGH, the RXPLL locks | ||||||||||||||||||

|

|

|

|

|

| to TRGCLKx± until they become valid. The SDASEL[A..D][1:0] inputs configure | ||||||||||||||||||

|

|

|

|

|

| the trip level of the Signal Level Detector. The Transition Density Detector limit is | ||||||||||||||||||

|

|

|

|

|

| one transition in every 60 consecutive bits. When LDTDEN is LOW, only the | ||||||||||||||||||

|

|

|

|

|

| Range Controller determines if the RXPLL tracks TRGCLKx± or the selected input | ||||||||||||||||||

|

|

|

|

|

| serial data stream. Set LDTDEN = HIGH. | ||||||||||||||||||

|

|

|

|

| LVTTL Input, | Use Local Clock. When |

|

|

|

| is LOW, the RXPLL locks to TRGCLKx± instead | |||||||||||||

| ULCA | ULCx | ||||||||||||||||||||||

| ULCB | internal pull up | of the received serial data stream. While | ULCx | is LOW, the | LFIx | for the associated | |||||||||||||||||

| ULCC |

| channel is LOW, indicating a link fault. | |||||||||||||||||||||

| ULCD |

| When |

|

| is HIGH, the RXPLL performs Clock and Data Recovery functions on | ||||||||||||||||||

|

| ULCx | ||||||||||||||||||||||

|

|

|

|

|

| the input data streams. This function is used in applications that need a stable | ||||||||||||||||||

|

|

|

|

|

| RXCLKx±. When valid data transitions are absent for a long time, or the | ||||||||||||||||||

|

|

|

|

|

| differential serial inputs (INx±) are left floating, the RXCLKx± outputs may briefly | ||||||||||||||||||

|

|

|

|

|

| be different from TRGCLKx±. | ||||||||||||||||||

| SPDSELA | Serial Rate Select. The SPDSELx inputs specify the operating | ||||||||||||||||||||||

| SPDSELB | static control input | range of each channel’s receive PLL. | |||||||||||||||||||||

| SPDSELC |

| LOW = | |||||||||||||||||||||

| SPDSELD |

| ||||||||||||||||||||||

|

| MID = | ||||||||||||||||||||||

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

| HIGH = | ||||||||||||||||||

|

|

|

| |||||||||||||||||||||

| INSELA | LVTTL Input, | Receive Input Selector. The INSELx input determines which external serial bit | |||||||||||||||||||||

| INSELB | asynchronous | stream passes to the receiver’s Clock and Data Recovery circuit. When INSELx | |||||||||||||||||||||

| INSELC |

| is HIGH, the Primary Differential Serial Data Input, INx1±, is the associated receive | |||||||||||||||||||||

| INSELD |

| channel. When INSELx is LOW, the Secondary Differential Serial Data Input, | |||||||||||||||||||||

|

|

|

|

|

| INx2±, is the associated receive channel. | ||||||||||||||||||

|

|

|

| LVTTL Output, | Link Fault Indication Output. |

|

|

|

| is an output status indicator signal. |

| is the | ||||||||||||

| LFIA | LFIx | LFIx | |||||||||||||||||||||

| LFIB | asynchronous | logical OR of six internal conditions. LFIx asserts LOW when any of the following | |||||||||||||||||||||

| LFIC |

| conditions is true: | |||||||||||||||||||||

| LFID |

| • Received serial data rate is outside expected range | |||||||||||||||||||||

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

| • Analog amplitude is below expected levels | ||||||||||||||||||

|

|

|

|

|

| • Transition density is lower than expected | ||||||||||||||||||

|

|

|

|

|

| • Receive is channel disabled | ||||||||||||||||||

|

|

|

|

|

| • |

| is LOW | ||||||||||||||||

|

|

|

|

|

| ULCx | ||||||||||||||||||

|

|

|

|

|

| • TRGCLKx± is absent. | ||||||||||||||||||

|

|

|

| |||||||||||||||||||||

| Device Configuration and Control Bus Signals | |||||||||||||||||||||||

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

| LVTTL input, | Control Write Enable. The |

|

|

|

|

| input writes the values of the DATA[7:0] bus | ||||||||||||

| WREN | WREN | ||||||||||||||||||||||

|

|

|

|

| asynchronous, | into the latch specified by the address location on the ADDR[3:0] bus.[3] | ||||||||||||||||||

|

|

|

|

| internal pull up |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ADDR[3:0] | LVTTL input | Control Addressing Bus. The ADDR[3:0] bus is the input address bus that | |||||||||||||||||||||

|

|

|

|

| asynchronous, | configures the device. The | WREN | input writes the values of the DATA[7:0] bus | ||||||||||||||||

|

|

|

|

| internal pull up | into the latch specified by the address location on the ADDR[3:0] bus.[3] Table 3, | ||||||||||||||||||

|

|

|

|

|

| “Device Configuration and Control Latch Descriptions,” on page 14 lists the config- | ||||||||||||||||||

|

|

|

|

|

| uration latches within the device, and the initialization value of the latches when | ||||||||||||||||||

|

|

|

|

|

| RESET is asserted. Table 4, “Device Control Latch Configuration Table,” on | ||||||||||||||||||

|

|

|

|

|

| page 16 shows how the latches are mapped in the device. | ||||||||||||||||||

Notes

2.Use

3.See “Device Configuration and Control Interface” on page 13 for detailed information about the operation of the Configuration Interface.

Document #: | Page 9 of 27 |

[+] Feedback