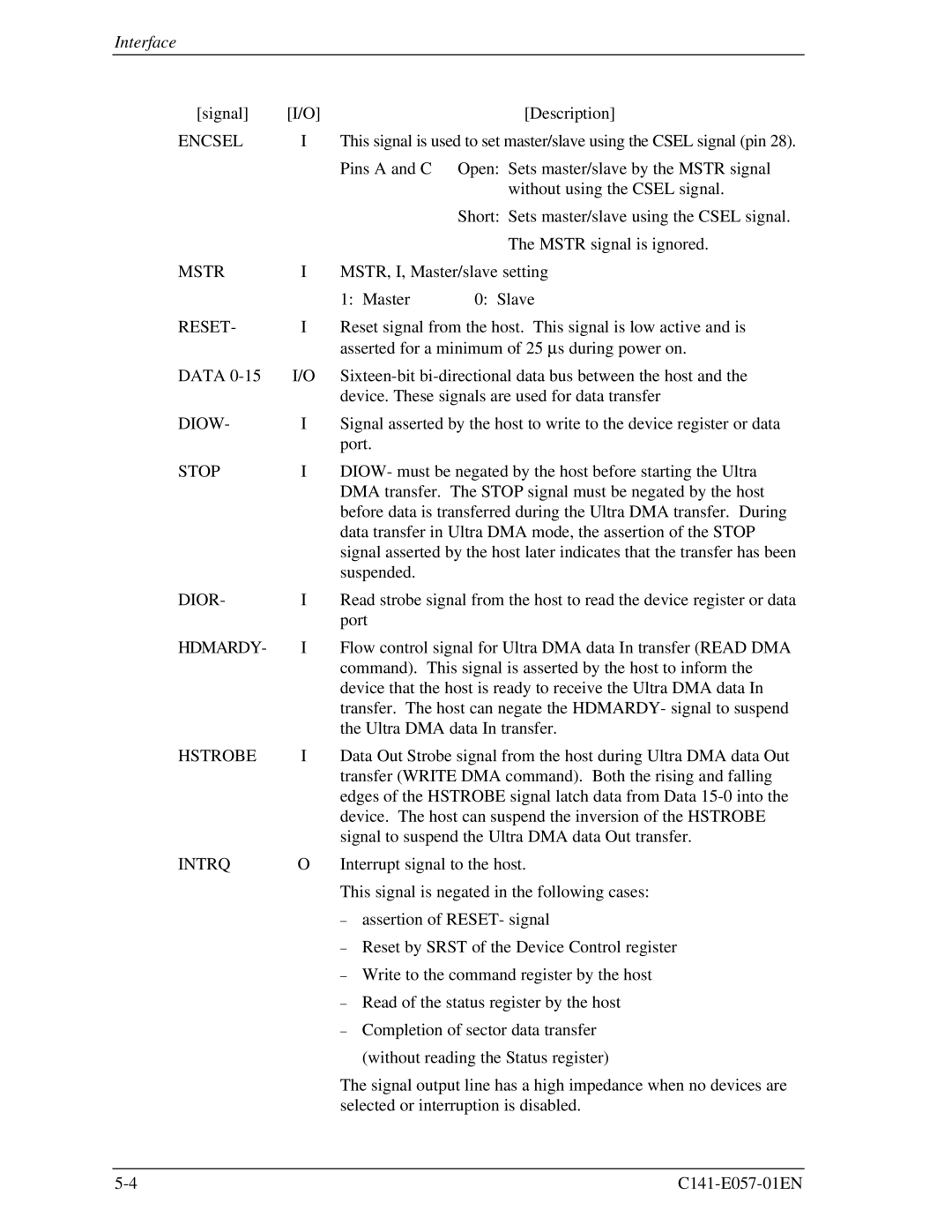

Interface

[signal] | [I/O] |

| [Description] |

ENCSEL | I | This signal is used to set master/slave using the CSEL signal (pin 28). | |

|

| Pins A and C Open: Sets master/slave by the MSTR signal | |

|

|

| without using the CSEL signal. |

|

|

| Short: Sets master/slave using the CSEL signal. |

|

|

| The MSTR signal is ignored. |

MSTR | I | MSTR, I, Master/slave setting | |

|

| 1: Master | 0: Slave |

RESET- | I | Reset signal from the host. This signal is low active and is | |

|

| asserted for a minimum of 25 μs during power on. | |

DATA | I/O | ||

|

| device. These signals are used for data transfer | |

DIOW- | I | Signal asserted by the host to write to the device register or data | |

|

| port. |

|

STOP | I | DIOW- must be negated by the host before starting the Ultra | |

|

| DMA transfer. The STOP signal must be negated by the host | |

|

| before data is transferred during the Ultra DMA transfer. During | |

|

| data transfer in Ultra DMA mode, the assertion of the STOP | |

|

| signal asserted by the host later indicates that the transfer has been | |

|

| suspended. |

|

DIOR- | I | Read strobe signal from the host to read the device register or data | |

|

| port |

|

HDMARDY- | I | Flow control signal for Ultra DMA data In transfer (READ DMA | |

|

| command). This signal is asserted by the host to inform the | |

|

| device that the host is ready to receive the Ultra DMA data In | |

|

| transfer. The host can negate the HDMARDY- signal to suspend | |

|

| the Ultra DMA data In transfer. | |

HSTROBE | I | Data Out Strobe signal from the host during Ultra DMA data Out | |

|

| transfer (WRITE DMA command). Both the rising and falling | |

|

| edges of the HSTROBE signal latch data from Data | |

|

| device. The host can suspend the inversion of the HSTROBE | |

|

| signal to suspend the Ultra DMA data Out transfer. | |

INTRQ | O | Interrupt signal to the host. | |

|

| This signal is negated in the following cases: | |

|

| − assertion of RESET- signal | |

− Reset by SRST of the Device Control register − Write to the command register by the host

− Read of the status register by the host − Completion of sector data transfer

(without reading the Status register)

The signal output line has a high impedance when no devices are selected or interruption is disabled.