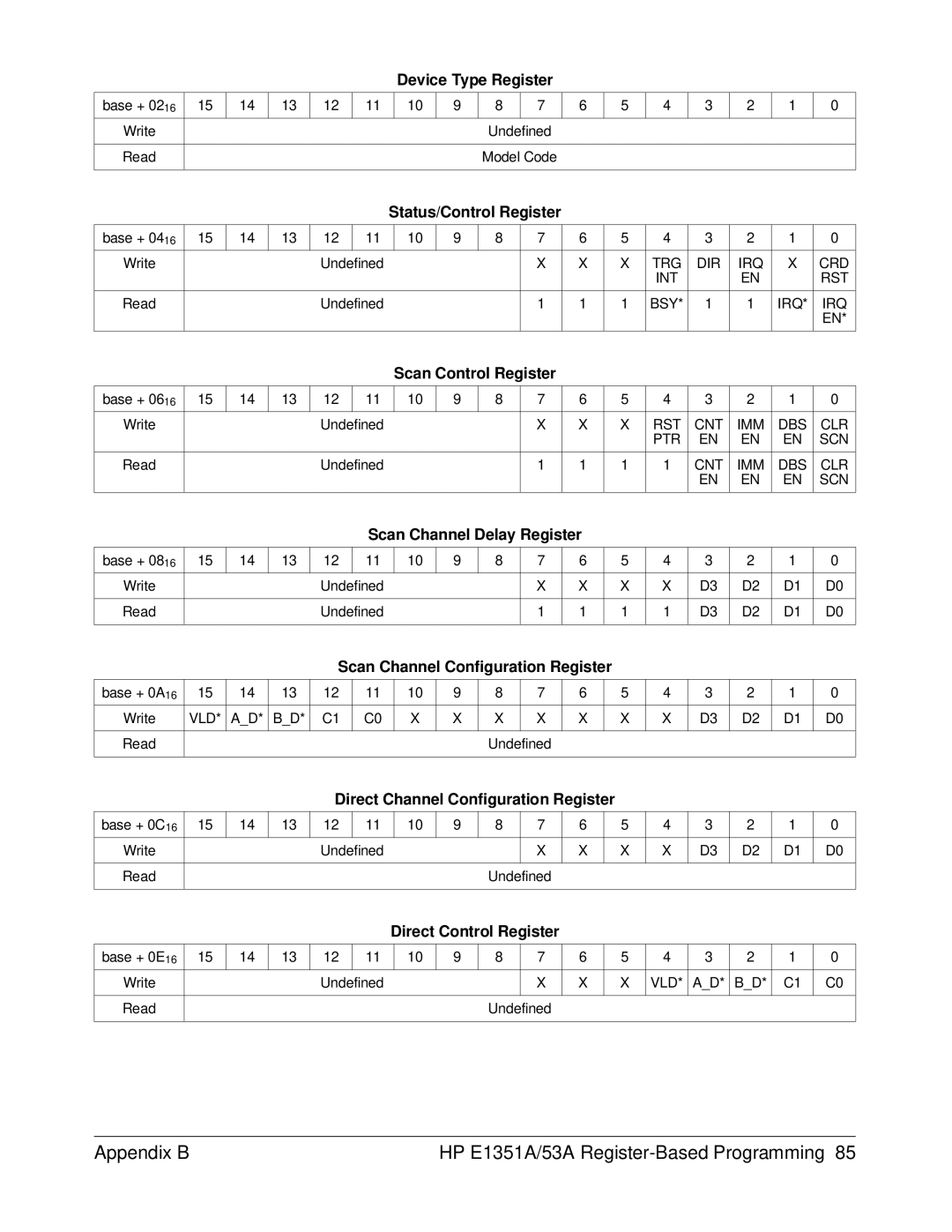

Device Type Register

base + 0216 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write |

|

|

|

|

|

|

| Undefined |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Read |

|

|

|

|

|

|

| Model Code |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Status/Control Register

base + 0416 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write |

|

| Undefined |

|

| X | X | X | TRG | DIR | IRQ | X | CRD | |||

|

|

|

|

|

|

|

|

|

|

|

| INT |

| EN |

| RST |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Read |

|

| Undefined |

|

| 1 | 1 | 1 | BSY* | 1 | 1 | IRQ* | IRQ | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| EN* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Scan Control Register

base + 0616 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write |

|

| Undefined |

|

| X | X | X | RST | CNT | IMM | DBS | CLR | |||

|

|

|

|

|

|

|

|

|

|

|

| PTR | EN | EN | EN | SCN |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Read |

|

| Undefined |

|

| 1 | 1 | 1 | 1 | CNT | IMM | DBS | CLR | |||

|

|

|

|

|

|

|

|

|

|

|

|

| EN | EN | EN | SCN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Scan Channel Delay Register

base + 0816 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write |

|

| Undefined |

|

| X | X | X | X | D3 | D2 | D1 | D0 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Read |

|

| Undefined |

|

| 1 | 1 | 1 | 1 | D3 | D2 | D1 | D0 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Scan Channel Configuration Register

base + 0A16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write | VLD* | A_D* | B_D* | C1 | C0 | X | X | X | X | X | X | X | D3 | D2 | D1 | D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Read |

|

|

|

|

|

|

| Undefined |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Direct Channel Configuration Register

base + 0C16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write |

|

| Undefined |

|

| X | X | X | X | D3 | D2 | D1 | D0 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Read |

|

|

|

|

|

|

| Undefined |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Direct Control Register

base + 0E16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write |

|

| Undefined |

|

| X | X | X | VLD* | A_D* | B_D* | C1 | C0 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Read |

|

|

|

|

|

| Undefined |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Appendix B | HP E1351A/53A |