Register Offset The register offset is the register’s location in the block of 64 address bytes. For example, with a LADDR of 112 the multiplexer’s Scan Channel Delay Register has an offset of 0816. When you write a command to this register, the offset is added to the base address to form the register address:

DC0016 + 0816 = DC0816 | (A16 outside the command module) |

1FDC0016 + 0816 = 1FDC0816 | (A16 inside the command module) |

or |

|

56,320 + 8 = 56,328 | (A16 outside the command module) |

2,087,936 + 8 = 2,087,944 | (A16 inside the command module) |

Register Descriptions

There are six WRITE and two

WRITE Registers The following WRITE registers are located on the multiplexer:

∙Status/Control Register (base + 0416)

∙Scan Control Register (base + 0616)

∙Scan Channel Delay Register (base + 0816)

∙Scan Channel Configuration Register (base + 0A16)

∙Direct Channel Configuration Register (base + 0C16)

∙Direct Control Register (base + 0E16)

READ Registers There are two

∙Manufacturer ID Register (base + 0016)

∙Device Type Register (base + 0216)

∙Status/Control Register (base + 0416)

∙Scan Control Register (base + 0616)

∙Scan Channel Delay Register (base + 0816)

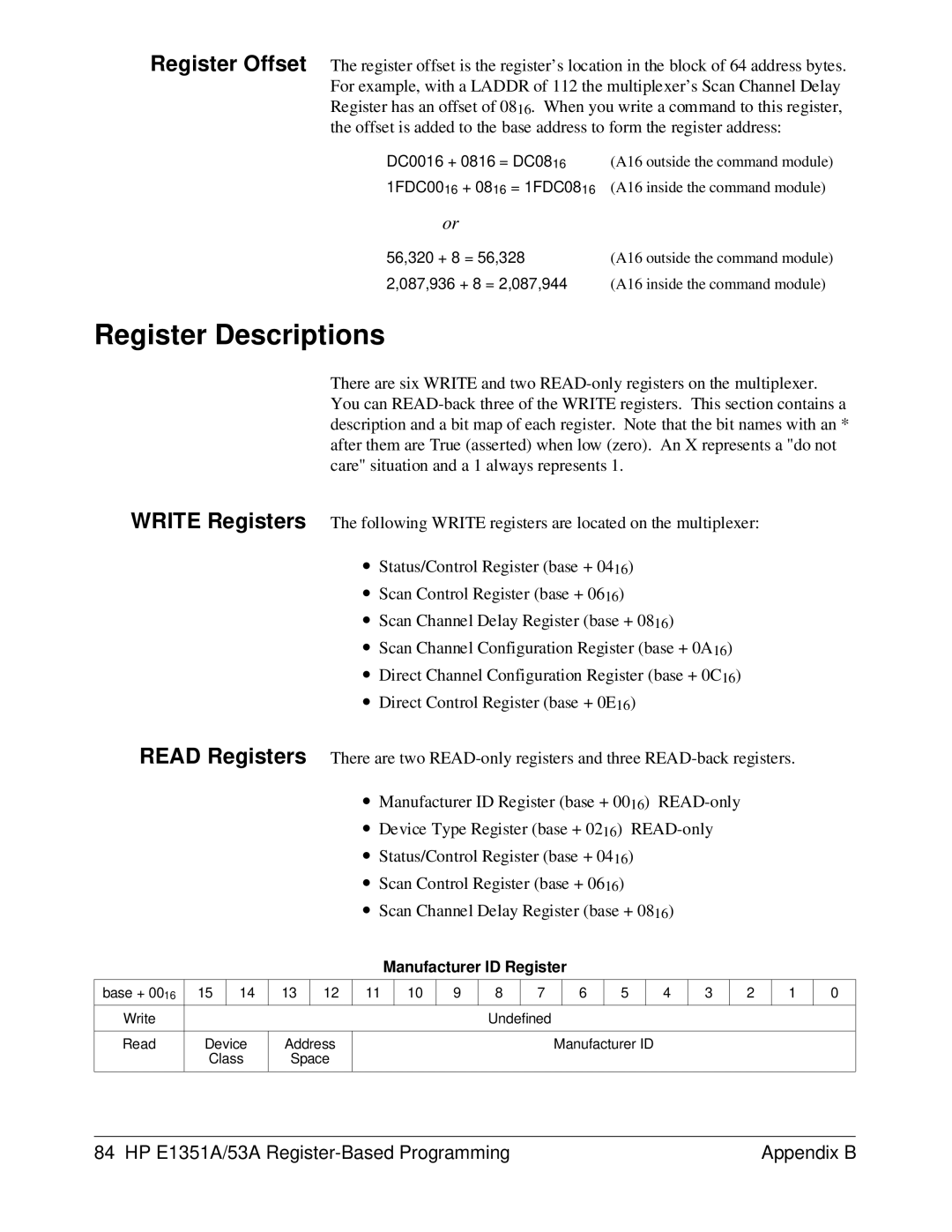

Manufacturer ID Register

base + 0016 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 |

| 6 | 5 |

| 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write |

|

|

|

|

|

|

| Undefined |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

Read | Device | Address |

|

|

|

|

| Manufacturer ID |

|

|

|

|

| |||||

| Class | Space |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

84 HP E1351A/53A | Appendix B |