Status/Control Register

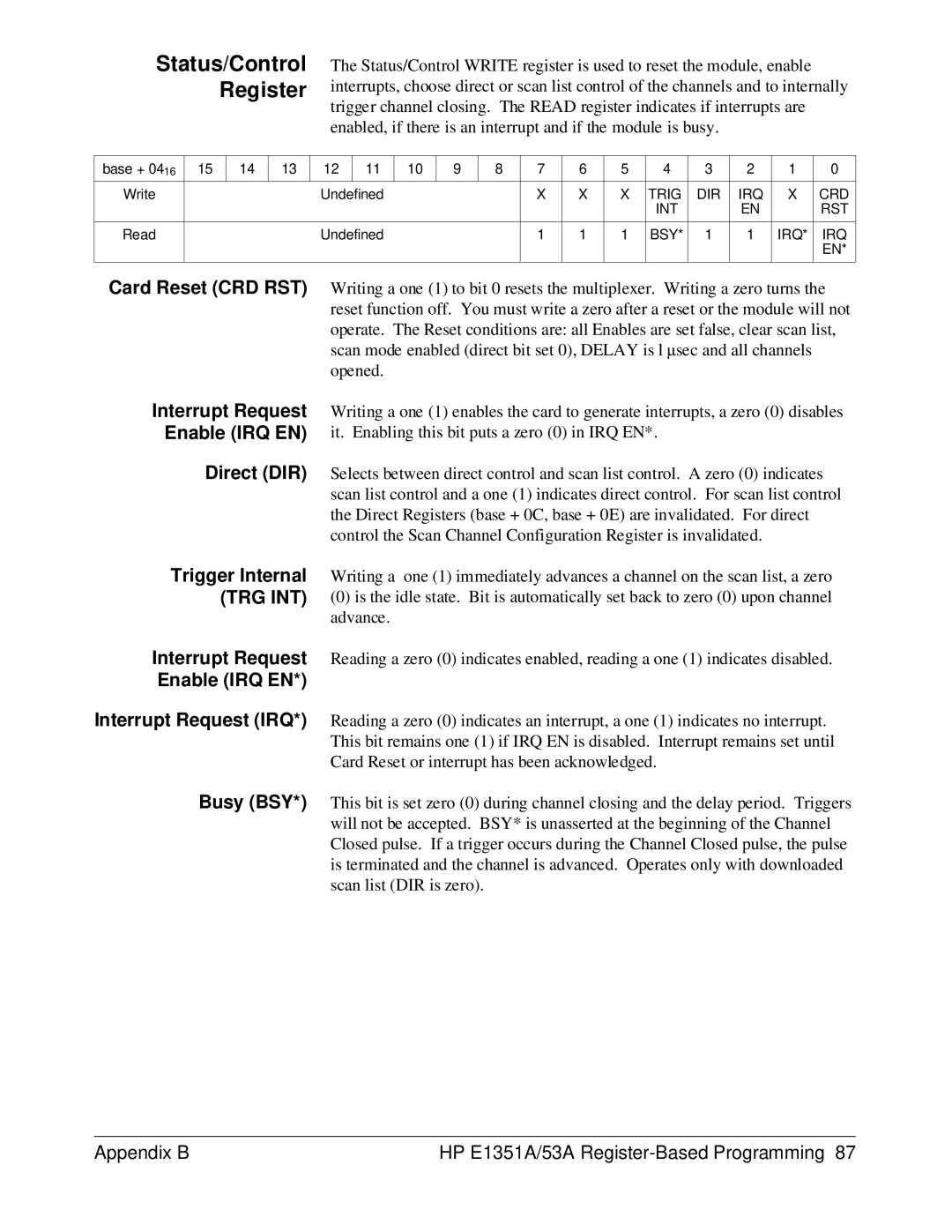

The Status/Control WRITE register is used to reset the module, enable interrupts, choose direct or scan list control of the channels and to internally trigger channel closing. The READ register indicates if interrupts are enabled, if there is an interrupt and if the module is busy.

base + 0416 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write |

|

| Undefined |

|

| X | X | X | TRIG | DIR | IRQ | X | CRD | |||

|

|

|

|

|

|

|

|

|

|

|

| INT |

| EN |

| RST |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Read |

|

| Undefined |

|

| 1 | 1 | 1 | BSY* | 1 | 1 | IRQ* | IRQ | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| EN* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Card Reset (CRD RST) Writing a one (1) to bit 0 resets the multiplexer. Writing a zero turns the reset function off. You must write a zero after a reset or the module will not operate. The Reset conditions are: all Enables are set false, clear scan list, scan mode enabled (direct bit set 0), DELAY is l μsec and all channels opened.

Interrupt Request Writing a one (1) enables the card to generate interrupts, a zero (0) disables Enable (IRQ EN) it. Enabling this bit puts a zero (0) in IRQ EN*.

Direct (DIR) Selects between direct control and scan list control. A zero (0) indicates scan list control and a one (1) indicates direct control. For scan list control the Direct Registers (base + 0C, base + 0E) are invalidated. For direct control the Scan Channel Configuration Register is invalidated.

Trigger Internal Writing a one (1) immediately advances a channel on the scan list, a zero (TRG INT) (0) is the idle state. Bit is automatically set back to zero (0) upon channel

advance.

Interrupt Request Reading a zero (0) indicates enabled, reading a one (1) indicates disabled.

Enable (IRQ EN*)

Interrupt Request (IRQ*) Reading a zero (0) indicates an interrupt, a one (1) indicates no interrupt. This bit remains one (1) if IRQ EN is disabled. Interrupt remains set until Card Reset or interrupt has been acknowledged.

Busy (BSY*) This bit is set zero (0) during channel closing and the delay period. Triggers will not be accepted. BSY* is unasserted at the beginning of the Channel Closed pulse. If a trigger occurs during the Channel Closed pulse, the pulse is terminated and the channel is advanced. Operates only with downloaded scan list (DIR is zero).

Appendix B | HP E1351A/53A |