®CompactPCI

3.22 J17 VGA Interface

J17 is available on the CPU

The controller uses a | 3 |

MHz RAMDAC and a |

All

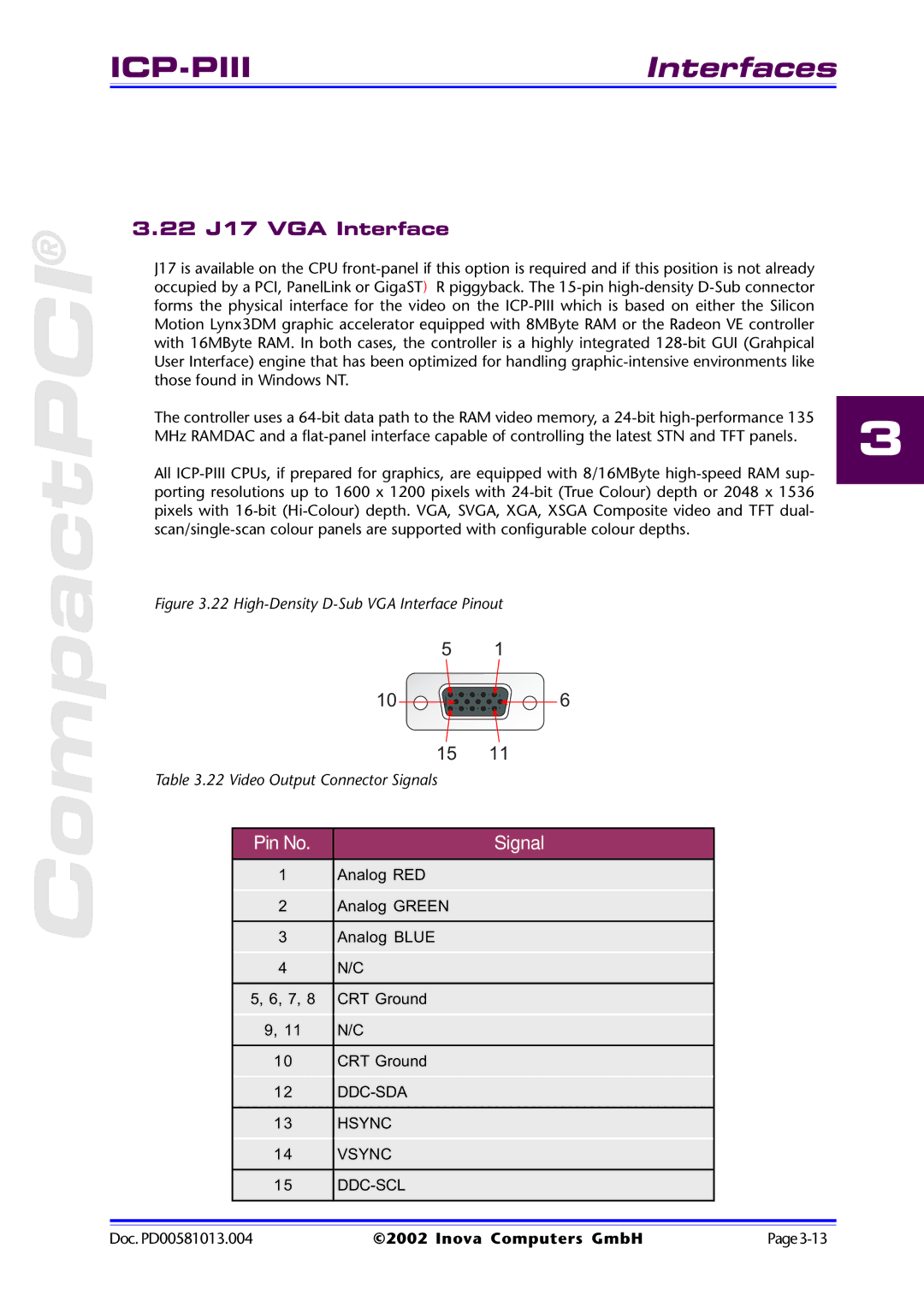

Figure 3.22 High-Density D-Sub VGA Interface Pinout

51

10

![]()

![]()

![]()

![]()

![]()

![]() 6

6

15 11

Table 3.22 Video Output Connector Signals

| Pin No. | Signal |

|

|

|

|

|

| 1 | Analog RED |

|

| 2 | Analog GREEN |

|

|

|

|

|

| 3 | Analog BLUE |

|

| 4 | N/C |

|

|

|

|

|

| 5, 6, 7, 8 | CRT Ground |

|

| 9, 11 | N/C |

|

|

|

|

|

| 10 | CRT Ground |

|

| 12 |

| |

|

|

|

|

| 13 | HSYNC |

|

| 14 | VSYNC |

|

|

|

|

|

| 15 |

| |

|

|

|

|

|

|

|

|

|

|

|

|

Doc. PD00581013.004 | ©2002 Inova Computers GmbH |